引 言

大部分FPGA采用基于SRAM(静态随机存储器)的查找表逻辑形成结构,就是用SRAM构成逻辑函数发生器。SRAM工艺的芯片在掉电后信息就会丢失,需要外加一片专用配置芯片。在上电时,由这个专用配置芯片把数据加载到FPGA中,然后FPGA就可以正常工作。这就是在线可重配置ICR(In-Circuit Reconfigurability)方式。

Altera公司生产的具有ICR功能的APEX、FLEX10K、ACEX、FLEX6000等系列器件可以使用6种模式进行配置,即使用专用EPC配置器件、被动串行(PS)方式、被动并行同步(PPS)方式、被动并行异步(PPA)方式、被动串行异步(PSA)方式及边界扫描(JTAG)方式。这些模式由FPGA上的两个模式选择引脚MSEL1和MSEL0上的电平来决定。

EPC配置器件有一次性可编程和可擦写编程型两种。一次性可编程型芯片不适于调试、修改及产品升级,利用率不高;可擦除编程型芯片价格昂贵,容量有限。使用PS、PPS、PPA方式配置时,配置文件要以二进制形式保存在系统ROM中,然后通过微处理器将配置数据送进FPGA中。PS和PPS所用的配置时间几乎相同,而PS的接口方式比较简单。PPA方式与PPS不一样的地方是在进行串行化处理时不需要配置外部时钟的驱动,但接口更复杂。边界扫描方式在现场采用较少,通常用在计算机通过JTAG口实现一次性编程数据加载的调试中。 以上6种模式中被动串行(PS)方式下FPGA与配置电路的互连最简单,对配置时钟的最低频率也没有限制,因此常采用PS模式。本文采用单片机P89C61X2以PS模式对Altera公司的FLEX10K系列芯片EPF10K20进行配置,软件采用MAX+PLUS II。

1 P89C61X2的功能特点

P89C61X2器件采用高性能的静态80C51设计,使用先进的CMOS工艺制造,并包含非易失性Flash的程序存储器,可通过并行编程或在系统编程(ISP)的方法进行编程。支持6时钟和12时钟模式,相应地有2种速度范围:6时钟模式时,0~20 MHz;12时钟模式时,0~33 MHz。

P89C61X2包含64 KB的Flast程序存储器、1 024字节RAM、32个I/O口、3个16位定时/计数器、6中断源-4中断优先级-嵌套的中断结构、1个增强型UART、片内振荡器和时钟电路等。此外,器件的静态设计使其具有非常宽的频率范围,甚至可以降低至零。P89C61X2具有两种软件可选的节电模式--空闲模式和掉电模式。空闲模式时冻结CPU的运行,但允许RAM、定时器串口和中断系统继续保持其功能;掉电模式时保持RAM的内容,但冻结振荡器,使其他片内功能都停止工作。由于是静态设计,时钟停止也不会使用户数据丢失。操作可从时钟停止点恢复运行。

P89C61X2的Flash存储器增加了EPROM所没有的电可擦除和编程特性,可以进行芯片擦除和块擦除。芯片擦除操作是将整个程序存储区都擦除;而块擦除可实现对任意Flash块进行擦除。对P89C61X2进行在系统编程和标准的并行编程都是可行的。片内产生的擦除和写入时序为用户提供了良好的编程接口。P89C61X2的Flash存储器甚至在经过10 000次擦除和编程之后仍能可靠地保存存储器内容。使用+5 V的Vpp即可实现对其进行擦除和编程。

2 配置原理和配置文件

用单片机通过PS模式配置FPGA,可以使用单片机的普通输入/输出(I/O)口(如图1(a)所示)或串行口(如图1(b)所示)来实现。配置中使用了FPGA的nCONFIG(配置控制位输入端)、nSTATUS(配置错误指示位输出端)、CONF_DONE(配置结束标志位输出端)、DCLK(配置时钟输入端)、DATA0(配置数据输入端)引脚等。nCEO引脚用于多个FPGA器件采用PS模式配置时,把第一片的nCEO连接到下一片的nCE引脚上。配置时若使用普通I/O口(如P1口),向FPGA发送1位数据至少需要4个指令周期:一个指令给DATA0赋值,两个指令产生DCLK时钟,一个指令移位取数据。如果晶振频率为fosc,一个指令周期为12/fosc,那么它的下载速率为fosc/48。如果采用串行口方式0,其下载速率提高为fosc/12。P89C61X2支持6时钟模式,速度可以提高一倍。

在配置过程中,nCONFIG低电位使EPF10K20复位,在由低到高的跳变过程中启动配置;加电后,EPF10K20驱动nSTATUS引脚到低电位,然后释放它(nSTATUS必须经过1 kΩ电阻上拉到VCC,若配置期间出错,EPF10K20将其拉低),每个数据由最低位(LSB)先送出给DATA0,数据时钟DCLK同时送到器件,直到CONF_DONE变高。在所有数据传输完后,对于FLEX10K和FLEX6000器件,DCLK必须多送10个DCLK脉冲;APEX20K器件必须多送40个DCLK脉冲。EPF10K20的CONF_DONE变高显示配置成功,开始初始化,最后进入用户模式,开始正常工作。由于PS模式中没有握手信号,因此配置时钟的工作频率必须低于10 MHz,如果想在配置中中止,可以挂断DCLK。硬件描述语言生成的程序经MAX+PLUS II编译后会产生一个后缀为.sof的SRAM目标文件。该文件除配置数据外还含有控制字符,不能直接写人到PLD中去,需要利用MAX+PLUS II的编程文件转换功能。例如有些编程器支持.rbf文件。.rbf文件为原始二进制文件,该文件包括所有的配置数据,配置文件的大小一般由它决定。1字节的.rbf文件有8位配置数据,每一字节在配置时最低位最先被装载。不同系列的目标器件配置数据的大小也不同,如.rbf文件在FLEK系列中,EPF10K10为15 KB,EPF10K20为29 KB,EPF10K30为46 KB,EPF10K40为61 KB,EPF10K70为109 KB等。由于P89C61X2包含64 KB Flash程序存储器,可以对除EPF10K70外的其他器件实现配置,而大干61 KB的FPGA器件可采用扩展存储器的方法来实现。

MAX+PLUS II不自动生成.rbf文件,须按照下面的步骤生成:①在MAX十PLUS II编译状态下,选择文件菜单的变换SRAM目标文件命令;②在变换SRAM目标文件对话框中指定要转换的文件并且选择输出文件格式为.rbf,然后确定。

针对单片机P89C61X2,可以通过在系统编程(ISP)的方法实现。这里采用广州致远电子有限公司开发的在线编程下载软件ZLGICD。该软件支持.hex文件。.hex文件为十六进制文件,MAX+PLUS II编译时会自动生成该文件,如果没有也可采用类似产生.rbf文件的方法生成。

用P89C61X2来配置FPGA,需将引导配置代码(.hex文件)和FPGA的配置数据(.hex文件)一起通过编程器写入P89C61X2。配置数据需要改变现有地址来让引导程序调用,否则会造成冲突。可以自己编写一个小程序来实现此功能。注意.hex文件的格式。由于引导配置代码不长,通常小于1 KB,因此有足够的空间来存放配置数据。

3 软件设计

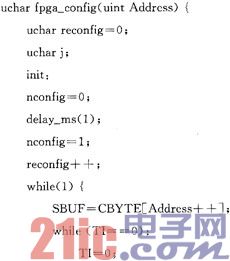

软件编程时,本系统只用到了串行口移位寄存器的输出方式,串行数据通过RXD引脚输出,移位时钟由TXD引脚输出。当有一个字节数据写入串行数据缓冲器SBUF时,开始发送。而串行口输出方式本身就满足配置时最低位(LSB)先送出的要求。下面给出用C语言编写的子程序:

结 语

用P89C61X2单片机来配置FPGA,从价格上来看,要优于EPC配置器件;从时间上来看,采用串行口方式0配置EPF10K20不到1秒钟,而用单片机的普通输入/输出口方式要慢许多;从使用上来看,不扩展存储器使电路连线更加简单。另外,单片机与FPGA优势相结合也给产品开发提供了更多更优的选择方案。