1.引言

随着永磁同步电机在工业、农业、航天等各领域的广泛应用,永磁同步电机在电动汽车驱动系统领域也得到同步发展。众所周知,永磁同步电机的稳定可靠运行,需要安装位置传感器来检测位置信号。因旋转变压器(简称旋变)通过与相应的解码芯片配合即可对电机转子位置进行检测,所以旋变作为较为可靠的绝对位置传感器被广泛采用。目前很多专家学者开始研究旋变位置解码系统[1-4],随着旋变及其解码芯片技术的不断发展,旋变的可靠性更高,解码电路也更加紧凑。本文采用当前最新一代可变磁阻旋变和与之配合的解码芯片AD2S1205,设计了相应的旋变位置解码系统,并通过测试系统验证了系统的可靠性。

2.旋变工作原理

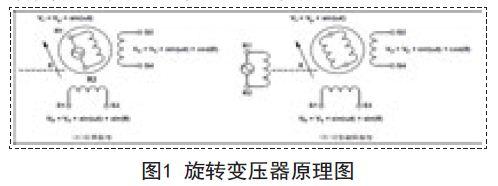

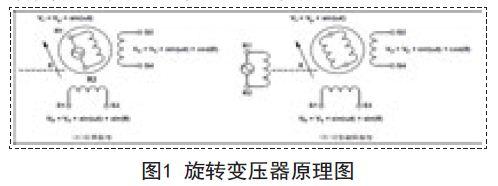

旋变的通常配置是初级绕组位于转子上,两个二次绕组位于定子上。本系统采用的可变磁阻旋变的转子上则不存在绕组,如图1所示,初级绕组和二次绕组均位于定子上,转子的这种特殊设计可使得次级耦合随着角位置变化而发生正弦变化。

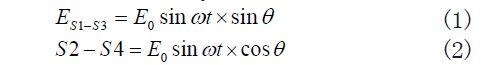

无论何种配置,旋变正弦绕组的输出电压是S1-S3,余弦绕组的输出电压是S2-S4,如(1)式和(2)式所示。其中:θ为轴角,ω为转子激励角频率,E0为转子激励幅度。

可变磁阻旋变初级绕组采用交流基准源激励,两个次级绕组机械上交叉90°。定子二次绕组上耦合出的电压幅度是转子相对于定子角位置θ的函数,旋变输出信号如图2所示。

转换器跟踪轴角θ的原理为,转换器产生输出角φ,然后反馈φ以与输入角θ相比较。当转换器正确跟踪输入角度时,二者之间的误差将被驱动至0。为了测量误差,将(1)式乘以cosφ,(2)式乘以sinφ,其差值为:

当角度误差(θ-φ)的值很小时,(4)式即近似等于0E(θ-φ)。AD2S1205具备一个由相位敏感解调器、积分器和补偿滤波器形成的闭环系统,可力求使误差信号归零。当该目标实现时,在转换器的额定精度范围内,输出角φ即等于旋变角度θ。

3.硬件电路设计

硬件电路的设计是围绕AD公司的解码芯片AD2S1205展开的。首先,该芯片是一款完整的12位分辨率跟踪分解器数字转换器,内置可编程正弦波振荡器,为旋变提供正弦波激励,工作频率范围为8.192MHz±25%。该芯片采用Type II跟踪环路,可用于跟踪输入信号,并将正弦和余弦输入端的信息转换为角度和速率所对应的数字量,其最大跟踪速率是外部时钟频率的函数。Type II跟踪环路能够连续输出位置数据,且没有转换延迟,它还能提供噪声抑制,以及参考和输入信号的谐波失真容限。

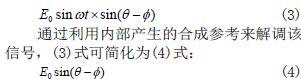

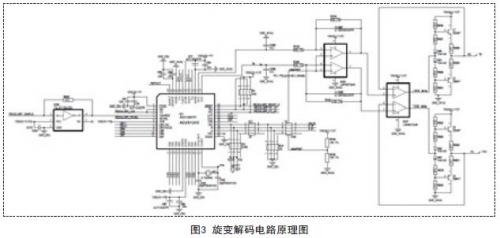

图3为旋变解码电路原理图。首先由AD2S1205解码芯片产生差分正弦励磁信号,经过运放放大、跟随后,通过推挽的方式输出到电机旋变。电机旋变返回的差分信号S1-S3、S2-S4,经IC26运算后送AD2S1205进行处理。SINLO和COSLO同时接入到REFOUT的目的是增强信号的稳定性,信号放大倍数为1.5。

针对故障检测,芯片内部有相关的故障检测功能,其相关故障的优先等级和故障码如表1所示。

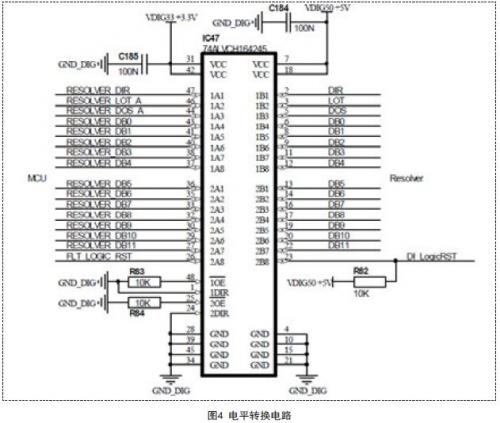

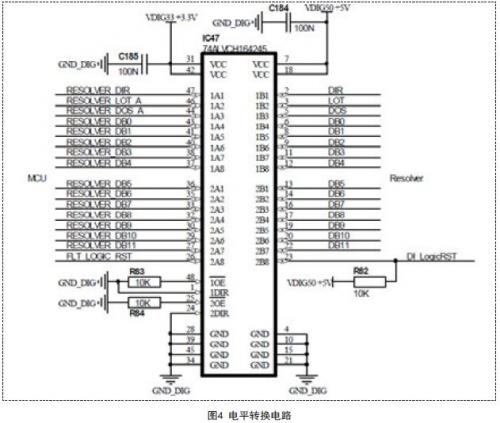

电平转换芯片采用74ALVCH164245,此芯片把旋变信号转为3.3V后送单片机,其电路如图4所示。

4.软件设计

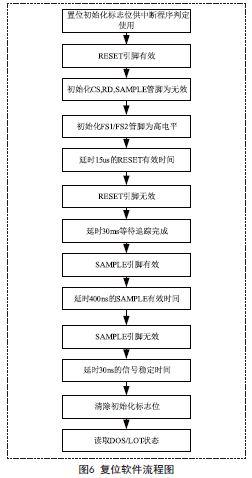

4.1 复位时序

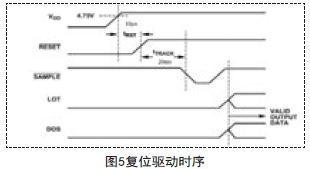

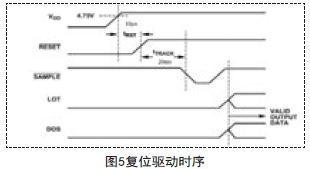

图5为AD2S1205复位驱动时序。

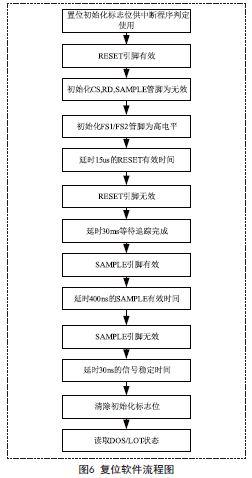

当AD2S1205的电源电压小于4.5V时,AD2S1205处于低电压复位状态,LOT/DOS同时为低电平指示,系统复位无信号。当电源电压超过4.5V以后,RESET管脚需保持有效电平至少10μs以上,使得AD2S1205芯片复位。在复位无效后,AD2S1205需要至少20ms时间,使得内部电路能够稳定工作,并且追踪电路能够稳定追踪输入角度。经过20ms的稳定工作时间后,SAMPLE有效并且保持一段时间,复位软件流程如图6所示。

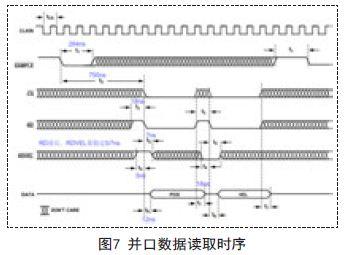

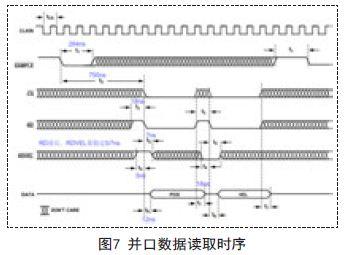

4.2 并口数据读取时序

图7为通过并行接口读取AD2S1205数据的驱动时序。并口数据读取时序从SAMPLE有效开始,SAMPLE必须保持264ns有效时间,锁存内部角度/速度数据至角度/速度寄存器中,然后在SAMPLE有效后750ns,MCU才能控制CS管脚有效,使锁存允许,并采用RD的下降沿锁存角度/速度寄存器中的一项数值内容至数据管脚(并口模式)。RDVEL决定锁存角度寄存器还是速度寄存器,所以在RD下降沿的前5ns和后7ns,RDVEL必须保持稳定不变。在RD下降沿,延时12ns后,即可从并口读取角度数据或者速度数据。

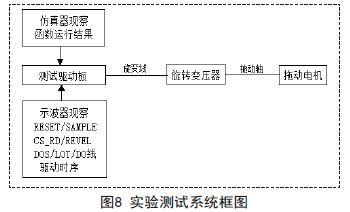

5.实验结果

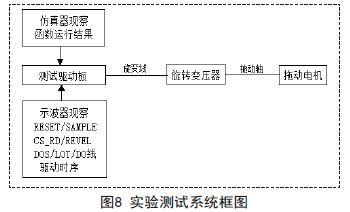

实验测试系统由测试驱动板,旋变和拖动电机组成,如图8所示。拖动电机旋转带动旋变运行于不同的转动角度和转动速度上,由解码电路输出励磁信号,驱动旋变,同时接收反馈的正、余弦信号,解析旋变的转动角度和转动速度。通过使用仿真器,在初始化函数的前后设置断点控制函数调试过程,并观察函数运行结果是否正确。通过示波器,观察函数运行后相关管脚上的驱动时序是否正确,并观测RESET/SAMPLE/LOT/DOS管脚。在初始化执行过程中,需参照复位时序观察MCU控制的RESET和SAMPLE管脚是否在对应时间送出对应电平或者脉冲,需观察如果系统硬件连接正常,DOS/LOT管脚是否在初始化后输出高电平指示,或者如果系统硬件连接不正常(比如旋变接线断路),DOS/LOT管脚是否在初始化后输出对应故障信号。

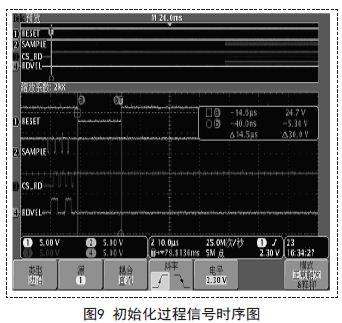

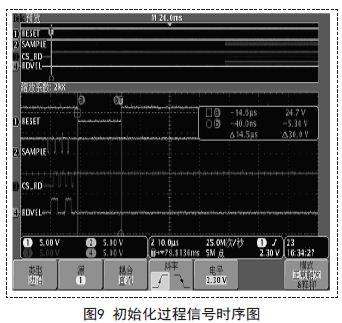

图9为AD2S1205的初始化函数调用时的总图。

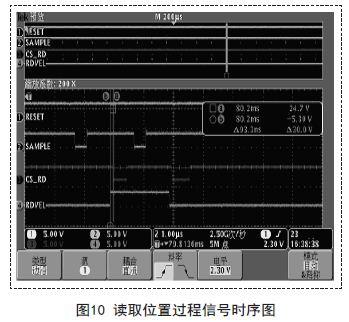

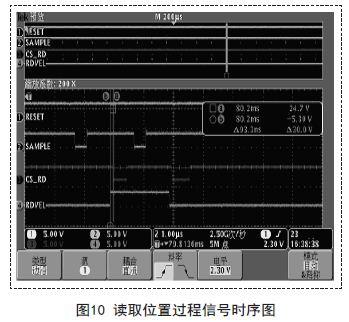

框a为开始调用初始化函数的时间点位置,在这个时间点,RESET管脚送出15μs的复位有效低电平脉冲,同时置高SAMPLE/CS_RD两路管脚为无效高电平。框b为结束初始化函数的时间点位置,在这个时间点,SAMPLE送出400ns采样有效低电平脉冲,然后读取DOS/LOT状态供应用层使用。初始化函数整体时间为30ms,即RESET复位结束到SAMPLE有效读取DOS/LOT状态的延时时间为30ms。读取位置测试程序每100μs调用一次角度函数和速度函数,测试结果如图10所示。

图10中SAMPLE有效时间为427ns;SAMPLE无效时间至读取角度/速度延时为750ns;RDVEL管脚选择读取角度/速度的延时为90ns;CS_RD有效时间为480ns,基本反映出从CS_RD下降沿至读取角度/速度的延时时间,CS_RD无效至下一次读取时间为200ns。

因此,测试所得AD2S1205的读取角度函数,与其驱动时序符合。测试所得AD2S1205的读取速度函数,与其驱动时序符合。通过仿真器验证,测试程序读取得到的角度值和速度值,也均符合预期。

6.结论

本文基于旋变及其解码芯片的原理和特点,提出了一种旋变位置解码系统的设计方案。试验结果表明,本方案的硬件和软件设计均满足电机位置解码要求,并且时序正确。

畅学电子

畅学电子

![[四轴飞行器教程]适合新手的简单PID调节方法,任何飞控通用](/Uploads/2014_12/video/vi8fc8d028840bfa6c191d73d8eafcc08b_s.jpg)