1 引言

近几年来,随着计算机网络技术的快速发展,TCP/IP协议已成为应用最广泛的网络互联协议。USB(通用串行总线)以灵活、方便、通信稳定、成本低廉、即插即用等优点已经成为数据存储与交换的通用接口。

ADChips公司的32位多媒体微处理器VirgineG2(简称VG2)具有强大的数据、图像和音频处理功能,而且能够直接输出NTSC/PAL制式模拟信号。VG2只提供了一路32位的I/O接口和两路串行通讯接口,因此需要对VG2扩展TCP/IP接口和USB接口,以实现远/近程数据的交互和大容量数据存储。

本文采用Realtek公司的RTL8019AS芯片对VG2进行以太网接口扩展,通过TCP/IP协议规范及LwIP实现VG2的TCP/IP协议栈。同时采用Philips公司的ISP1161芯片实现VG2的USB主/从控制接口扩展。

2 VG2的以太网和USB硬件接口设计

2.1芯片简介

VG2内嵌16/32位(EISCSE3208)多媒体微控制器,内含2路4 KB的Cache、2D图像加速器,32通道的8/16位音频处理器以及DAC、DRAM,控制器、DMA、定时器、双串口等多种外设。还具有8个外部片选信号(PCS0#一PCS7#)和27个中断源,其中包括8个外部中断(IRQ0~IRQ7)。基于3D的2D图形加速器支持NTSC/PAL制式电视显示。

RTL8019AS是Realtek公司生产的以太网接口控制器,符合NE2000标准,遵循IEEE802.3协议。支持8位、16位的数据总线,有即插即用、跳线和免跳线三种工作方式。RTL8019AS内置16 KB RAM,用作收发缓冲以降低对主处理器的请求频率。内部还有远程DMA通道和本地DMA通道。

ISP1161是Philips公司生产的通用串行总线(USB)主机控制器(HC)和设备控制器(DC),遵循USB 1.1,支持全速(12 Mbit/s)及低速(1.5 Mbit/s,)两种数据传输模式。两个USB控制器在使用中共用一个微处理器总线接口,但I/O地址不同,并有各自的中断请求输出引脚和独立的DMA通道。ISP1161提供两个下行端口和一个上行端口.每一个下行端口都有一个过流(OC)检测输入引脚及电源开关控制输出端,上行端口也有自身的VBUS检测输入端。另外还提供了单独的唤醒输入端和挂起输出端。HC的下行端口能与USB兼容设备及具有USB上行端口的USB集线器连接。

2.2 VG2的TCP/IP和USB接口设计

2.2.1硬件设计

对VG2扩展USB接口和以太网接口的硬件原理框图如图1所示。

以太网接口设计中。VG2的PCS6和IRQ6分别作为RTL8019AS的片选信号和中断信号。RTL8019AS其他引脚连接方式为:JP接高电平,设置RTL8019AS工作在跳线方式下;IOS3~IOS0接低电平,设置其I/O基地址Ox300,这样RTL8019AS只对地址为0x300~0x31F的信号产生响应;IRQS2~IRQS0接低电平,INT0被选中作为中断请求的输出;PL1、PL0接低电平,设置具有自动检测接口类型的功能。

当PCS6有效时,VG2为RTL8019AS映射从0x0160 0000开始的1 MB内存,SA8和SA9位为高电平,对应于RTL8019AS的地址线信号为0000 0000 0011 000X XXXX,I/O基址设置为0x300。这样通过地址的低5位就可以读取RTL8019AS内部的32个寄存器。对VG2控制映射RTL8019AS内部寄存器地址为0x0160 0000+相应的偏移地址(0x00~Ox1F)。

2.2.2 USB接口设计

VG2采用PCS7和IRQ7分别作为ISP1161的片选信号和中断信号,ISP1161采用I/O通信的方式,其I/O地址如表1所列。

ISP1161寄存器是一个指令-数据双重结构寄存器。一个完整的寄存器访问周期首先为指令阶段,然后为数据阶段。指令(也可以理解为寄存器的指针)指向ISP1161的下一个将被访问的寄存器。一个指令为8位长,在一个微处理器的16位数据总线上,指令占用低字节,高字节被填充为0。微处理器先向指令端口写入一个指令代码.然后从数据端口读/写数据字。

当PCS7有效时,VG2为ISP1161映射从0x1700 0000开始的1 MB内存。ISP1161主机控制器的数据和命令地址分别是Ox0170 0000和Ox0170 0002,设备控制器的数据和命令地址分别是0x0170 0004和0x0170 0006。

3软件设计

系统的软件部分通过在VG2中嵌入实时多任务操作系统μC/OS一Ⅱ来实现。在μC/OS一Ⅱ平台上分别对各个接口进行多任务的控制。

3.1 μC/OS-Ⅱ移植

μC/OS一Ⅱ是一个完整、可移植、固化、裁剪的占先式实时多任务内核。如果只保留其最核心的代码,则可压缩到3 KB。将μC/OS-Ⅱ移植到VG2微处理器上需改写与硬件相关的汇编语言。具体改写内容如下所示:

(1)改写OS_CPU.H中部分函数

#define OS_TASK_SW() asm("swi 7"),通过软件中断指令来实现操作系统的任务切换函数:#defi-neOS_ENTER_CRITICAL()asm("clrl3"),#define OS_EXIT_CRITICAL asm("set 13"),通过对SR状态寄存器的中断控制位设置实现使能或禁止操作系统响应中断请求;#define OS_STK_GROWTH 1,定义VG2的堆栈由高到低。

(2)改写OS_CPU_C.C中部分函数

OSTaskStkInit()为任务栈结构的初始化函数。VG2响应中断请求信号后,将当前寄存器值按先入后出的顺序压入堆栈。

OSTaskStkInit()按照压入堆栈顺序对各任务栈初始化。

OSStartHighRdy()函数跳转到所有处于就绪状态任务中优先级最高的任务开始运行。操作系统首先得到最高优先级任务栈的指针,然后从任务栈中弹出所有寄存器值,实现跳转。

OSCtxSw()是任务级的任务切换函数。swi 7(软件中断)的中断向量指向该函数。当需要任务切换时,首先该函数将当前任务寄存器值压入堆栈。然后将当前任务任务栈指针保存到任务控制块中。最后判断出最高优先级任务,并弹出其任务栈内容,开始运行。

OSTickISR()为操作系统提供一个周期性的时钟源。VG2的定时器0被设定成第20 ms发出一个时钟中断信号,中断向量指向该函数。首先该函数保存当前任务状态,并将全局变量OSTime递增1。然后判断出最高优先级任务.并弹出其任务栈内容,开始运行。

OSIntCtxSw()为系统执行中断后任务调度函数。系统在中断响应后执行该函数判断出最高优先级任务,然后弹出其任务栈内容,开始运行。

3.2以太网接口的TCP/IP协议移植

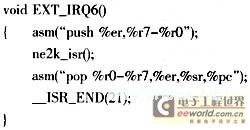

由于嵌入式实时操作系统μC/OS-Ⅱ是一个操作系统内核,本身没有集成TCP/IP协议栈,所以需要移植合适的TCP/IP协议栈。LwIP协议栈是适用于8位、16位、32位微处理器嵌入式系统的一个小型TCP/IP协议栈,实现了ARP、TCP、UDP、IP这些最基本的协议。LwIP可以看作是为系统提供的函数,通过它来进行数据包的发送与接收。LwIP允许有多个网络接口,每个网络接口都对应一个structnetif,而且都包含相应网络接口的属性和收发函数。其中netif->input()指向IP层的接收函数ip_input(),netif->output()指向ne2k_send_packet()驱动程序中的发送函数。驱动程序可实现网络接口的接收、发送、初始化以及中断处理。本设计中采用中断方式来接收数据,使用VG2的外部中断INT6,在VG2的中断向量表中可以按照如下定义:

3.3 USB接口的PTD协议移植

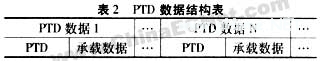

VG2与ISP1161之间以PTD(Philips Transfer Descriptor)数据格式进行通信。PTD数据提供了USB通信的相关信息,如指令、状态和USB数据包等。VG2中PTD数据的物理存储介质是微处理器的系统RAM。对于ISP1161,存储介质为内部FIFO缓冲区RAM。ISP1161可使用PTD数据结构定义一块数据缓冲区,使其与USB终端设备进行通信。VG2设立这个数据缓冲区采存放当前帧(1 ms帧)。每帧传送的承载数据必须包含一个PTD作为传输头,以描述传输特性。PTD数据一般为DWORD(双字或4字节)格式,结构如表2所示。

PTD数据头为8个字节的数据结构,包含了ISP1161的传输类型、装载数据的发送位置、装载数据的实际大小、传输速度、传输对象等。当传输执行完毕后。其内部会作相应的改变,在PTD数据头中表征了本次传输结果.包括传输发生的错误信息等。

3.4部分程序流程

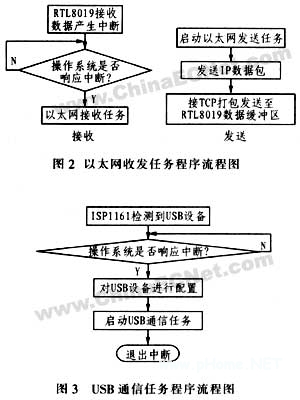

以太网收发任务程序流程如图2所示。USB通信任务程序流程如图3所示。

本设计采用的操作系统是实时操作系统,可以同时支持以太网通信和USB设备数据存储,系统能获得很高的效率和稳定性。

4 结束语

本文采用RTL8019AS通过TCP/IP协议规范及LwIP,实现了VG2的TCP/IP协议栈,通信波特率可达到10Mb/s。同时采用Philips公司的ISP1161,实现VG2的USB主/从控制接口扩展,符合USB1.1规范,通信速率可达到1.5Mb/s。该设计用于所研制的数字化家居智能控制器,通过以太网、USB和其他接口,将家用电器、家庭安防、门禁、四表自动抄表、有线电视网、电话和宽带网系统等独立单元的家居设施跨平台有机结合,实现远/近程操作控制和数据存储与交换。