电路板上电源的数量取决于VLSI所使用的多个电源的数量,它们与其它器件之间的通信速度需要电路板上有一套独特的电源,如使用的存储器类型。这是因为每个VLSI(ASIC/ SoC)器件需要多个电源才能正常工作(如核电压、I / O电压、PLL电压、SERDES通道电压,以及存储器接口电压)。结果,电路板上有15至25个电压的情况并不少见。多个电源的电路板通常需要实现电源管理功能,包括电源定序、电源故障监测、微调和裕度调整。有些电路板可能需要增强的电源管理功能,如电压升降调整,电源故障的非易失性记录和后台时序更新。

电路板电源管理的要求

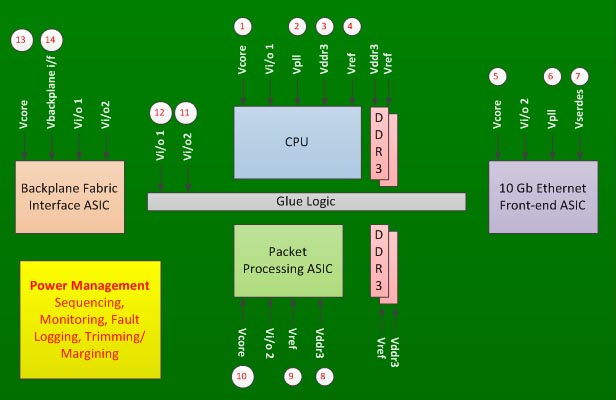

在图1所示的线卡中,有四个主要的集成电路和一些粘合逻辑。每个集成电路都需要多个电源,并有定序的要求。这块电路板有14个电源电压,需要进行监测、定序、微调和裕度调整。此外,电路板的设计还需要将任何意想不到的电源故障记录在非易失性存储器中。

最初设计电路板的电源管理算法时,设计人员通常只考虑器件相关的时序。这是因为电路板设计人员不知道不同电压的电源定序的相互依存关系。在一般情况下,在调试过程中要确定电源定序,可编程定序解决方案应该能够适应原来的定序算法的以下变化:

- 开启每个电压或一组电压之间的时间延迟

- 重新定序- 例如如果原来设计的序列为1,2,4,5,3,那么新的顺序应该能够定序为2,3,5,1,4

- 关闭电源的定序-以相反的顺序关闭电源(这是必要的,以尽量减少损坏集成电路)

- 最大限度地减少集成电路(需要多个电压)部分被供电的情况,这取决于给定器件的电源故障。例如,如果电源3有故障,那么要立即关闭电源4,然后关闭电源1和2。如果电源1有故障,那么按顺序关闭电源2,3,4。

- 生成电源良好的指示,使各种器件开始工作。例如,CPU需要电源良好的信号,不仅内核电压是好的,而且DDR存储器电压,PLL和IO电压都是好的。

- 能够监测数字信号来完成定序。例如,在给DDR电源上电之前,等待数据包处理ASIC的PLL锁定。

- 通过数字控制信号(或逻辑组合)根据需要启动电源关闭,例如,前面板关机信号。

图1 -通信线路卡的主要集成电路和电源的要求

所有的电源都打开之后,电路板开始正常工作,电源管理部分应开始监测电源的故障。当任何一个电源出现故障,然后根据发生故障的电源,CPU应该中断或复位以防止闪存损坏。电源管理算法的监测部分应该具有以下特点:

- 以1%或更好的精度确定任何按装在电路板上的电源的故障,以尽量减少虚假的故障指示,最大限度地减少由于监控器的精度限制而错过了电源故障。此故障指示可用于产生中断复位到CPU。

- 由于电源管理电路和装在电路板上的电源之间存在地电压差,使用差分信号检测较低的电源电压(1.5V或以下),以尽量减少错误。

- 在100毫秒内报告故障,最大限度地减少由于故障电源引起的数据和/或指令的持续时间。

- 将故障与监控信号相联系。例如,如果电源1,2,3或4有故障,就激活复位信号。但是,如果电源12有故障,只中断CPU,以防止传输错误的数据。

故障记录功能应该记录整个电路板断电的主要原因。通常在一块电路板上的初始故障会引发连锁反应。例如,如果电源1有故障,电路板关机功能开始根据编程的电源关闭顺序关闭其余的电源。如果故障记录电路对电源故障的反应速度足够快,捕获的情况将显示电源1有故障,以及其余的电源工作正常。但如果故障记录电路的响应时间缓慢,它会记录电源2,3和4都有故障。这样的故障情况是没用的。故障记录电路应具有以下特点:

- 准确找到任何电源故障(<1%的误差),以增加捕获的故障情况的可靠性

- 在100微秒内启动故障记录过程,尽量减少原始故障对捕获情况的后续影响。

电源管理实现示例

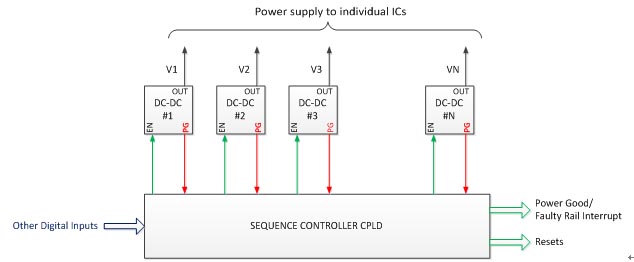

一个实现复杂的电源管理的常用方法(图2)是使用DC-DC转换器的电源良好信号,以监测这个电源,并使用CPLD来实现定序算法(控制DC-DC转换器的使能信号)。CPLD也产生监测信号,如电源就绪/故障电压中断和复位信号。

图2:使用电源良好信号对比电源管理监测实际电源电压

优点:

- 满足所有的定序要求

- 电源的数量可扩展

- 电源上电或电源关闭的定序算法的大小/复杂性没有限制

- 定序算法可以与电源定序之间的监控信号(电源良好/故障电压指示)交错

- 由任意数量的数字输入控制定序和监测算法

- 在现场系统可以更新定序算法而不中断电路板的工作

缺点:

- 有效的“电源良好”信号并不意味着电源工作在集成电路正常工作的范围内。大多数DC-DC转换器的电源良好信号有8%至20%的监测误差。但是大多数集成电路的电源容差是在3至5%之间。例如,1.2V电压的实际电压(核电压)可以低于额定值的10%(1.08V),但DC-DC转换器电源良好信号可以指明电源是好的,CPLD可能未激活其复位信号。因此,CPU可能会挂起,并重写闪存的一个部分(闪存讹误)。DC-DC转换器的电源良好信号不应该被用来作为电源电压故障指示,产生监控信号,诸如“复位”或“低电压中断”。

- 即使电源电压处于运行容差之前,通常一些集成电路是能够工作的,。因此,定序算法等待一个额外的时间,使该集成电路板可靠地启动。

- 增加软件的调试时间- 由于精度差的CPU的电源良好信号和存储器电源,会发生闪存讹误的情况。很难区分是软件错误,还是由于故障电源引起的意想不到的程序执行情况。因为没有办法确定硬件的电源故障,在归咎于故障电路板之前,软件工程师浪费了时间,责怪由于闪存讹误产生了软件错误。这可能会导致产品发布时间的延迟。

用Platform Manager实现分布式检测和集中控制

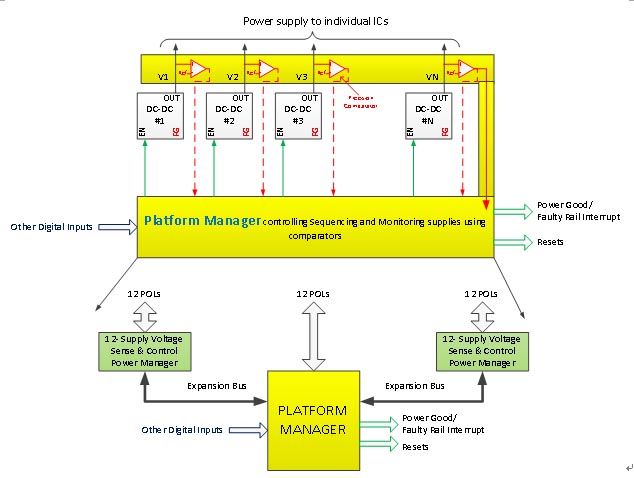

图3展示了远程传感和实施集中控制。这种架构类似图2所示的电路方案。由于比较器和ADC的整合,这种方案需要的元件数量最少。此解决方案使用了一片莱迪思的Platform Manager和两片莱迪思的Power Manager集成电路,实现了多达36个电压的电源管理。

莱迪思的Platform Manager器件集成了对12个电源电压的监测,一个48宏单元的CPLD和一个640 LUT的FPGA。Power Manager器件可用于检测和控制多达12个负载电源。整个电源管理算法在Platform Manager内的FPGA部分实现。Platform Manager还支持电源的微调和裕度调整。

图3使用Platform Manager的分布式电压检测和集中控制

优点:

- 完全灵活的定序支持多达36个电压,因为在FPGA内实现中央电源管理。对每个电源故障情况的时间调整或定序响应没有限制。

- 可靠无折衷的产生灵活的监控信号,因为电压监测精度为0.7%。此外,因为Platform Manager 和Power Manger器件支持差分电压检测,精度不会因为电路板任何部分之间的接地电压差而受到影响。

因为所有电源故障状态都被发送到FPGA,对任何故障的算法响应用100微秒的时间,能够立即产生监控信号。这样的速度,再加上很高的监测精度,最大限度地减少了闪存讹误的机会。

- 电路板上任何电源故障或其他任何故障可以在100微秒内记录到非易失性存储器。这将确保故障捕获情况中包含了主要故障。

- 电源管理算法可以使用HDL代码实现或使用简化的算法开发工具,称为LogiBuilder来实现。可以对该程序充分进行模拟,对算法可以进行微调:最大限度地减少电路板由于错误而重新返工的风险。

电源管理算法可以在系统内更新,而不中断电路板的工作。该器件还存储了一个“golden image”,所以如果在系统更新被中断,电路板的电源被重新启动,该电路板使用这个golden image重新工作。

Platform Manager 和the Power Manager之间的通信很简单,莱迪思提供了参考设计。用户只需添加此参考设计到实际的电路板的电源管理算法。该参考设计提供自动管理所有器件之间的通信,而不干预主要电源的管理算法

总结

要求CPLD对电路板上超过12个电压实现电源管理功能,如定序,复位产生等功能。这些设计取决于电路板上按装的DC-DC转换器产生的电源良好信号,用以监控这些电压。然而,精度差的这些电源良好信号会导致电路板功能的可靠性大大降低。增加电路板的可靠性可以通过用精确的比较器替代这些电源良好信号,监控DC-DC转换器的实际输出电压。

本文阐述了一个可扩展、在系统可升级,星型拓扑结构的电源管理架构,能够满足在一块复杂的电路板上超过12个电压的电源管理要求。通过使用莱迪思的Platform Manager 和Power Manager器件,提高了电路板功能的可靠性,能够准确的监控DC-DC转换器的输出电压(使用片上精密比较器),而无需折衷FPGA内的电源管理算法。