1 引言

现代控制系统中控制对象可能是复杂、分散的,而且往往是并行、独立工作的,但整体上它们是相互关联的有机组合。因此,控制信号的时序逻辑则要求更加精确。CPLD" target="_blank">CPLD单片机为控制系统提供了技术支持,由CPLD和单片机组成的多机系统具有逻辑控制方便,时序精确,并行工作,人机接口友好等优点。因此,本文提出了一种基于CPLD与单片机控制的多路精确延时控制系统的设计方案。

2 设计指标与系统原理

2.1 设计指标

输出多路脉宽为10 ms正脉冲信号;

脉冲输出时间独立调节、显示;

时间调整范围与精度为微秒级的调整范围为l~199μs,调节精度为lμs;毫秒级的调整范围为1~199 ms,调整精度为1 ms;

提供计时基准信号和工作状态提示声音;

9 V电池供电。

2.2 系统设计原理

2.2.1 系统时钟

本系统设计由CPLD和多个单片机组成,CPLD对24 MHz高精度一体化晶体振荡器二分频得到多路同步时钟信号作为多个单片机的系统时钟,并由各个单片机外脉冲信号引脚XTAL2注入,二分频确保信号的占空比为50%,满足单片机时钟脉冲信号高低电平持续时间大于20 ns和最高脉冲频率为12 MHz的要求,同时也提高系统的可靠性。5l系列单片机采用定时控制方式,具有固定的机器周期,1个机器周期共有12个振荡脉冲周期,则机器周期是振荡脉冲的12分频。本系统采用12 MHz振荡脉冲频率,1个固定机器周期为1μs,因此能保证设计指标所要求的最高控制精度。

2.2.2 同步计时启动信号

本系统设计由外部按键提供启动信号,由于机械接触点的弹性及电压突跳等原因,按键存在抖动效应,为保证按键准确识别,本系统设计采用软件去抖动,再经单片机引脚输出无电压毛刺的稳定启动信号,再经CPLD变换后,可提供多路同步计时启动信号。

2.2.3 输出信号

本系统设计采用10 ms单脉冲信号作为各模块单元控制输出信号,其输出形式可根据需要通过软件调整,并保证系统输出信号的时序与逻辑关系。

2.2.4 系统时序

系统时序图如图1所示,在计时脉冲的驱动下,按键信号经去抖动变换、CPLD逻辑同步后形成计时启动信号(0一n),以计时基准脉冲的前沿为计时起点,经设定延时后,系统输出相应的输出信号,其延时时间可独立调整,信号输出形式可由软件编程设置。图l采用单一正脉冲作为输出信号。

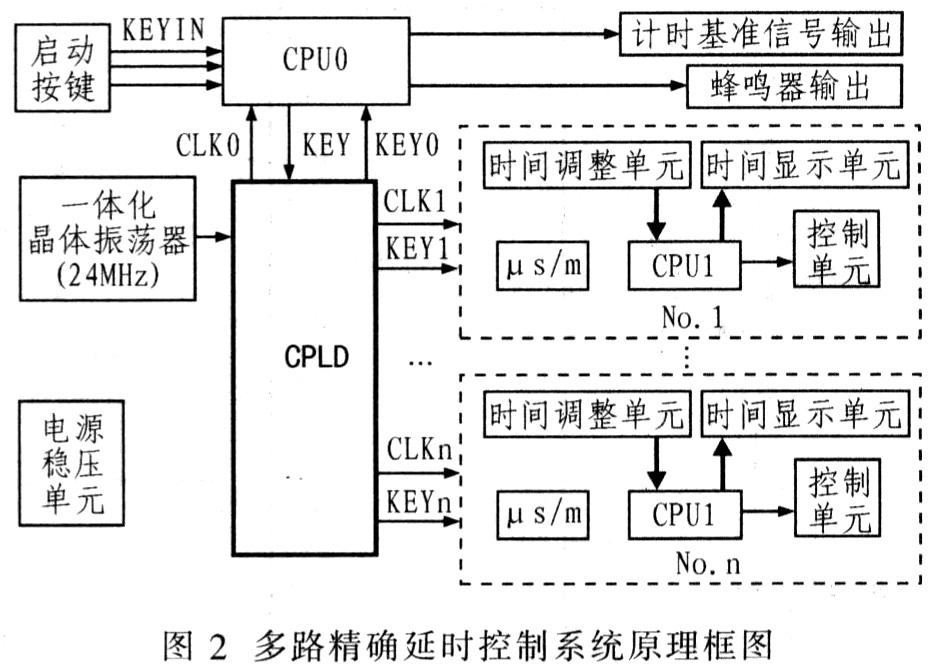

2.2.5 系统原理框图

电源稳压单元实现系统5 V电源的稳压与滤波。单片机采用外部系统时钟。主控单片机CPUO完成按键检测、计时基准信号输出和系统提示声音输出等功能。NO.1~N0.n单元完成时间调整与显示、μs/ms(微秒/毫秒)变换和信号输出等功能,CPLD完成时钟2分频、同步计时脉冲输出和计时启动信号同步输出功能。图2为多路精确延时控制系统原理框图。

3 硬件电路设计

3.1 主控单元

每个系统都由独立的主控单元组成,如图3所示。主控单元由电压、CPUO 和CPLD同步控制模块等组成。电压模块完成由可充电电池电压到稳定的5 V系统电源变换与滤波。CPUO单元模块选用ATMEL公司51系列单片机AT89S52A。AT89S52是低功耗、高性能CMOS 8位微控制器,具有8 KB在系统可编程Flash存储器、256字节的随机存取数据存储器(RAM)、32个外部双向输入/输出(I/O)端口、5个中断优先级2层中断嵌套中断、2个16位可编程定时计数器、2个全双工串行通信口,看门狗(WDT)电路,片内时钟振荡器,兼容标准MCS一5l指令系统。CPUO模块完成按键信号检测,工作状态提示音输出,计时基准信号输出等功能。CPLD同步控制模块采用ALTRA公司EPM7032SLC44为控制核心。 EPM7032SLC44是MAX7000 CPLD,是基于先进的多阵列矩阵(MAX)架构,采用先进的CMOS制造工艺,提供从32到512个宏单元的密度范围,速度达3.5 ns的引脚到引脚延迟。支持在系统可编程能力(ISP),可以在现场进行重配置。CPLD同步控制单元完成时钟分频与同步,按键信号同步等功能,ProKram插座是CPLD的编程接口。

3.2 输出控制单元

每个系统由n(本系统设计中n=9)个输出控制单元组成,这n个单元输出控制独立并行工作,如图4所示。N0.1~N0.n以ATMEL公司5l系列单片机AT89C2051为核心。AT89C205l是低功耗、高性能CMOS 8位单片机,具有15个双向输入/输出(I/O)端口、片内含2 K字节的可反复擦写的只读Flash程序存储器和128字节的随机存取数据存储器(RAM);采用ATMEL公司的高密度、非易失性存储技术生产,兼容标准MCS一5l指令系统。输出控制单元(NO.1~NO.n)并行工作,完成延时时间设置、μs/ms变换设置、控制信号输出和延时显示等功能,延时时间显示通过单片机串口实现,由3片串/并变换器件74LSl64驱动3个共阳数码管。

4 系统软件设计

本系统软件设计包括CPUO单元、NO.1~NO.n输出单元及CPLD单元程序设计。由于对时间要求严格,采用汇编语言编写,信号输出由中断程序完成,由于中断响应过程、现场保护以及中断后必要的设置条件检测需要时间,所以软件必须通过容余指令(比如NOP)的延时,可保证counter0输出和控制信号延时起点在同一时刻。

CPU0单元程序流程如图5所示。CPU0主程序完成系统初始化、按键检测、去抖动信号输出和工作状态提示音输出等工作,中断服务程序计时基准信号 counterO输出。输出控制单元NO.1一NO.n程序流程如图6所示,各单元主程序完成μs/ms设置检测,延时设置读取,延时时间显示,中断程序完成控制信号输出功能。CPLD程序采用VHDL语言编写,采用QHalftusⅡ软件编译仿真。

5 结语

该系统设计可应用于电容组(9只)放电控制系统,在放电电子开关控制端、负载端测量以及微秒级延时范围内,延时误差小于O.1μs,毫秒级延时范围内,延时误差小于50μs。实际测试显示,系统实现了设计要求的调整精度。基于单片机+CPLD的多路精确延时控制系统充分利用单片机和CPLD的各自特点,实现主要设计指标。实际应用证明,该系统能够完全满足时序逻辑要求中严格控制系统的控制需求。