在高速数字视频系统应用中,使用大容量存储器实现数据缓存是一个必不可少的环节。SDRAM就是经常用到的一种存储器。

但是,在主芯片与SDRAM之间产生的时序抖动问题阻碍了产品的大规模生产。在数字电视接收机的生产实际应用中,不同厂家的PCB板布线、PCB材料和时钟频率的不同,及SDRAM型号和器件一致性不同等原因,都会带来解码主芯片与SDRAM间访问时序的抖动问题。

本文利用C-NOVA公司数字电视MPEG-2解码芯片AVIA9700内置的SDRAM控制器所提供的时序补偿机制,设计了一个方便使用的内存时序测试软件工具,利用这个工具,开发测试人员可在以AVIA9700为解码器的数字电视接收机设计和生产中进行快速诊断,并解决SDRAM的时序问题。

数字电视系统

SDRAM时序控制

AVIA9700内集成了一个SDRAM控制器,该控制器提供一套完整的SDRAM接口。AVIA9700与SDRAM接口中的控制线、地址线和数据线都同步在MCLK时钟上。图1是用两片16位SDRAM组合形成32位数据线的典型连接示意图。

图1 SDRAM与AVIA9700典型链接示意图

SDRAM控制线

正确读写时序条件

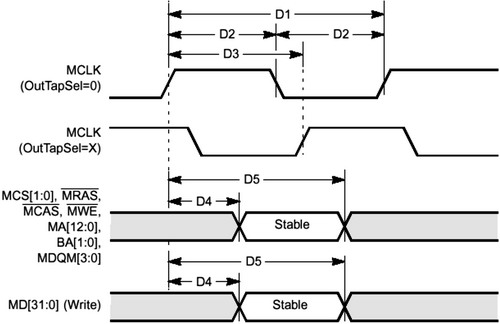

AVIA9700解码芯片访问SDRAM的时序如图2所示。

图2 AVIA9700访问SDRAM时序示意图

要正确访问SDRAM,建立时间和保持时间很关键。建立时间在触发器采样之前,在这段时间,数据必须保持有效的时间,否则会产生setup violation;保持时间在解发器开始采样之后,数据必须保持有效的时间,否则会产生hold violation。因此,要正确读写SDRAM的时序条件,需要满足以下两个公式:

SDRAM_Setup_time_min < T_cycle-control_signal_valid_max-control_signal_Delay_max+ clock_delay_min (1)

SDRAM_Hold_time_min < control_signal_valid_min + control_signal_delay_min- clock_delay_m_ax???? (2)

这里,T_cycle 为SDRAM时钟周期,Control signal valid为控制信号从时钟上升沿到输出有效时间,delay为布线所引起的延时。

对于低频设计,线互连和板层的影响很小,可以不考虑。当频率超过50MHz或信号上升时间Tr小于6倍传输线延时时,互连关系必须以传输线理论纳入考虑之中,而在评定系统性能时也必须考虑PCB板材料的电参数。由于AVIA9700输出时钟信号MCLK工作在108MHz~148.5MHz之间,所以设计时必须考虑布线延时引起的SDRAM时序问题。

AVIA9700 SDRAM

时序控制机制

为了补偿布线延时,满足公式(1)和公式(2)的要求,AVIA9700的内置SDRAM控制器提供了两个延时补偿参数:SDRAM_CLK_IN 和SDRAM_CLK_OUT。这两个参数都是8位的整数,可以提供不同的时钟延时组合,解决各种复杂数字电视接收机系统中的SDRAM时序问题。

通过嵌入式应用软件,开发人员可以调整SDRAM_CLK_IN的参数来控制读入数据的时钟延时。同样,对SDRAM_CLK_OUT的设置也可以改变输出时钟的延时。通过设置SDRAM_CLK_OUT (OutTapSel=X)改变输出的MCLK时钟相位,补偿各种不同的布线延时,可以解决高速数字电视系统的SDRAM时序问题。

在实际应用中,由于不同整机厂会采用不同厂家的SDRAM,PCB布线也会因为机器结构原因发生较大变化,时钟工作频率和选用器材的不一致性等,都会引起公式(1)、(2)中的参数发生变化。这些因素的组合,往往使布线延时问题变得复杂。

AVIA9700 SDRAM

时序诊断软件及测试结果

为了方便开发人员快速解决问题,本文利用AVIA9700内置SDRAM控制器提供的时钟延时补偿机制,设计了一个诊断工具。

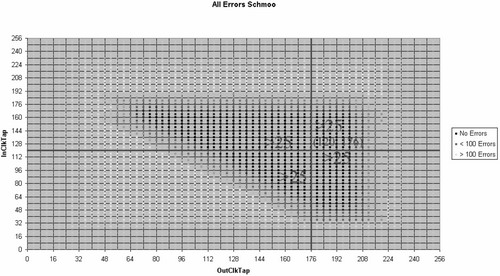

基于AVIA9700数字电视接收机,由于PCB、元器件、系统频率都已经定型,影响布线延时的电气特性已经固化。通过改变 SDRAM_CLK_IN和SDRAM_CLK_OUT组合,设计人员可以测试不同组合下的SDRAM访问错误率,根据错误率统计数据制成统计图,如图3 所示。图中纵坐标为SDRAM_CLK_IN,由于寄存器是8位,因此选取坐标取值范围在0~255之间(28);横坐标为SDRAM_CLK_OUT,取值范围也在0~255之间。对该范围内的某一点所对应的寄存器设置,诊断软件都要自动重复10000次读写操作。设计人员可以利用最后生成的图形,快速准确地选定SDRAM_CLK_IN和SDRAM_CLK _OUT的值,并将其固化在最终生产版本的软件中。

图3 SDRAM时序测试统计图

这里,补偿参数的选择原则是,组合值需要在测试图中无错区域的中心,且距离边界大于25。

结语

通过实验发现,在高速数字系统设计中,通过SDRAM控制器来补偿布线延时可以很好地解决SDRAM时序问题。

参考文献

1. Howard Honson, Martin Graham. 高速数字设计[ M ] . 电子工业出版社. 2004

2. AVIA9700 datasheet C-NOVA, Inc. 2004

3. AVIA9700 programming guide C-Nova, Inc. 2004