应用材料((Applied Materials Inc., AMAT)公司日前宣布在Endura Volta CVD Cobalt系统中通过化学气相沉积方法,在铜互连工艺中成功实现钴薄膜沉积。这一被业界视作“15年来铜互连科技中最大材料变革”的创新方案,突破了导线互联技术传统瓶颈,得以让“摩尔定律”持续向下进展到20纳米及更先进制程。

对于当前高性能移动应用处理器、微处理器和服务器芯片厂商来说,为了实现产品的低功耗、高性能和强可靠性,芯片通常包含10亿个以上的晶体管,采用9-15层金属层以实现晶体管间的互联,其消耗的铜线长度往往超过100千米。“目前系统芯片设计的最小互连仅为一根头发的1/2000,随着摩尔定律的推进,减少影响器件工作的空隙与防止电迁移失效就显得非常重要。”应用材料公司半导体产品事业部资深技术总监赵甘鸣博士说。

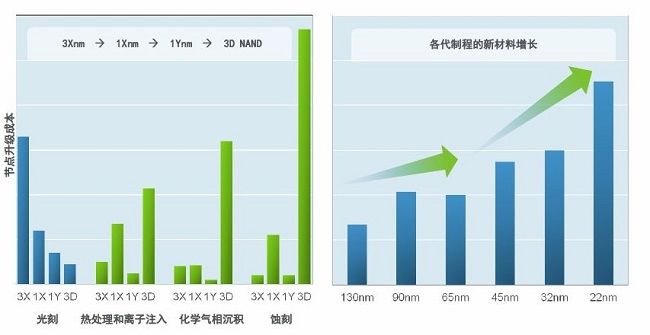

据统计,2010年-2013年晶圆设备产业已连续4年资本支出都达到300亿美元的规模,2014年更可望成长10%-20%。对此,赵甘鸣预测,2014年将是晶圆代工产业20纳米技术与3D NAND起飞量产的一年,3D存储器的发展将导致芯片代工企业的主要支出由光刻向材料沉积和去除转移,所使用的材料种类也大幅增加。另一方面,设备结构和制程技术也实现了大幅创新,从氮氧化硅(SiON)到28/32nm高K值金属栅极(HKMG),再到16/14nm 3D FinFET,应用材料公司在对应的商机规模可望有一定程度增加。

15年来,芯片代工企业一直在铜互联工艺中使用TaN/Ta薄膜,但当前更高的布线密度增加了工艺难度,业界迫切需要来自材料的创新。于是,具备低电阻率、与铜及阻挡层有很好的粘附性、铜浸润性好、可适用共形沉积或选择性沉积、适用于实际量产等优点的钴薄膜进入了AMAT的视野。“平整衬垫(Liner)与选择性覆盖层(Capping Layer)将是钴薄膜在铜工艺中的两种应用场景,有望将铜互连的可靠性提高一个数量级,并实现≤20nm铜线互连的完全封装。”赵甘鸣解释说,粘附性好,芯片可靠性就会大幅提升;浸润性好,新衬垫材料就可保证后续铜的完全填充。

基于Endura Volta CVD系统的钴工艺包括两个主要的工艺步骤。第一步是沉积一层平整的薄钴衬垫膜,相对于典型的铜互连工艺,钴的应用可为有限的互连区域填充铜提供更大的空间。这一步骤通过在同一平台超高真空下整合预清洗(Pre-clean)/阻挡层(PVD Barrier)/钴衬垫层(CVD Liner)/铜种子层(Cu Seed)制程,以改进器件的性能与良率;第二个步骤在铜化学机械研磨(Cu CMP)之后,沉积一层选择性CVD钴覆盖膜,改善接触界面,进而提高器件的可靠性可达到80倍。

钴薄膜沉积突破了导线互联技术传统瓶颈

全新PVD沉积系统实现高成本效益的3D芯片垂直集成

与Endura Volta CVD Cobalt系统同步推出的另一项创新技术,则是应用材料公司针对3D芯片垂直集成技术中出现的硅通孔(TSV)、再分布层(RDL)和凸块等应用推出的Endura Ventura PVD系统。应用材料公司表示,该新系统能够完成连续薄阻挡层和种子层的TSV沉积,帮助客户以更低廉的成本制造出体积更小、功耗更低的高性能集成3D芯片。此外,还与众不同地采用了钛作为阻隔材料,替代业内主流的钽阻挡层方案,从而实现降低成本的目的。

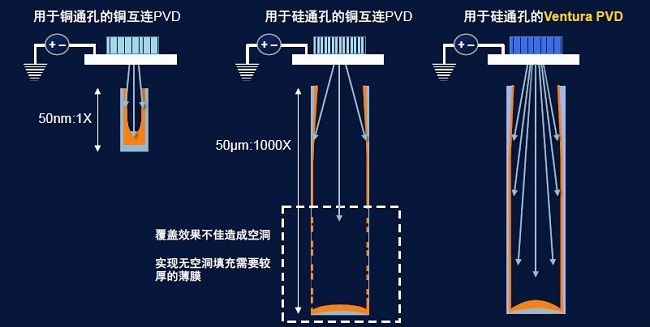

硅通孔是垂直穿过硅晶片的最短互联通道,可将设备的有源侧连接到硅片的背面。但从工艺角度来看,目前的制造难点集中在需要将大于10:1深宽比的TSV互连结构用铜进行金属化。“硅通孔具有完全不同的结构特征,TSV结构比铜通孔深1000倍。”赵甘鸣说,“如果你觉得不好理解,那我们用一个人的身高来比喻当前铜通孔深度,而在TSV结构中,硅通孔深度将达到6个埃菲尔铁塔的高度,足足增加了1000倍。”因此,确保阻挡层和种子层的完整性,实现芯片的可靠间隙填充和互连,继而有效提高3D芯片的良率,是此次Endura Ventura PVD系统着力实现的目标之一。

TSV结构的深度给目前的铜互联PVD系统带来挑战

目标之二则是解决硅通孔金属化带来的孔隙填充与成本控制之间的权衡,显然只有那些低成本、可靠的孔隙填充才能实现TSV量产。应用材料公司新技术上的突破能够显著改善离子的方向性,可在硅通孔中完成均匀连续的薄金属层沉积,从而实现TSV所需的无空隙填充。此外,由于方向性的改善,沉积速率也得以大幅提高,显著减少了阻隔材料和晶种材料的用量。与铜互连PVD系统相比,可使阻挡层和种子层成本降低多达50%。

Ventura PVD系统解决硅通孔金属化带来的孔隙填充与成本控制之间的权衡