国际标准化组织ISO和国际电信联盟ITU于2000年12月正式推出了JPEG2000标准,该标准采用以离散小渡变换为主的多解析编码方法,具有许多优良的特性,然而一直未获得广泛的应用。AD公司于2004年推出了能实时压缩和解压缩高质量运动图像和静止数字图像的JPEG2000编解码芯片ADV202。本文基于ADV202设计一个完整的嵌入式视频压缩系统,其中包括硬件电路设计和软件流程设计,该系统具有USB接口,支持热插拔,无需主机控制。

1 ADV202芯片介绍

ADV202是美国AD公司新近推出的一款用于视频和高带宽静止图像压缩的单片IPEG2000(ISO/IECl5444-1图像压缩标准)编解码芯片,是当今市场上惟一具有实时压缩和解压缩标准(SD)视频信 号和高清晰度(HDTV)视频信号的芯片,专利的空间高效递归滤波(SURF) 技术使其具有低功耗和低成本的小波压缩。它提供的专用视频接口可以无缝连接到删ITU.R-BT656,SMPTE125M、 SMPTE293M[525p]等标准的数字视频接口,灵活的异步SRAM风格的主机接口允许无缝连接到大多数16/32位的微控制器和ASIC器件。

ADV202的内部功能框图如图1所示,输入的视频或图像数据进入视频接口后经过解交错传输到小波变换引擎中。在小波引擎中,每帧图像或每个图块通过5/3或9/7滤波器分解成许多子带,生成的小波系数写入内部寄存器中。熵编码器将图像数据编码为符合JPEG2000标准的数据。内部DMA引擎提供存储器之间的高带宽传输以及各模块和存储器之间的高性能传输。内部FIFO提供像素数据、码流数据、特征数据和辅助数据的存储空间,既可由外部主机通过标准地址读写周期直接访问,也可以采用DREQ/DACK协议通过DMA方式访问或专用硬件握手机制访问。主机接口提供16/32位的控制总线和8/16 /32位的数据传输总线,用于对内部寄存器的配置、控制和状态传递以及压缩数据流的传输。

2 视频压缩系统硬件设计

2.1 系统硬件整体构架

系统硬件整体框架如图2所示,来自电视机或摄像机的单路PAL/NTSC制式的视频信号,经过SAA7n3编码为SAV/EAV模式、ITU.R—BT656 YUV4:2:2格式(8位)的视频信号,由VPO[7..0]传输到ADV202的视频接口。在ADV202内部,视频信号经过硬件编码产生.jp2格式的视频信号,由主机接口D[31..0]输入到TMS320VC33 DSP。经DSP压缩后的视频信号由USB接口芯片USBN9602转换后通过USB口输出。另外,DSP还通过数据总线D[31..O]和地址总线 A[3..]对ADV202内部直接及间接寄存器进行配置,加载ADV202编码模式所需的固件(由AD公司提供),对ADV202编码数进行设置。 USB口只作为压缩数据流的输出口,由DSP完全控制。

2.2 DSP小系统

出于对系统易实现性和性价比的考虑,DSP芯片选择Ⅱ公司的32位高性能数字信号处理器 TMS320VC33。TMS320VC33工作在75Mlk主频时,运算能力可达150MFLOPS,可以访问的总存储空间为16M×32bit,程序空间、数据空间和I/O空间都包含在整个16M×32bit空间中,且统一编址。片内提供了34K×32bit SRAM,考虑到系统处理对象是视频信号,要求较大的程序空间和数据空间,片内RAM通常不能满足系统要求,因而在DSP片外要进行存储器扩展。

DSP外部扩展了两片CY7C1041V33 (256K×16bit)SRAM和1片SST39VF400A(256K×l6bit)FLASH。两片CY7C1041V33按照数据位扩展方式扩展成为256K×32bit的数据存储空间,用于存储压缩后的视频数据。DSP工作在微计算机/引导模式(MCBL/MP=1)下,SST39VF400A 用于存储DSP的引导程序。

2.3 系统时序控制电路

系统时序控制电路由一片Altera EPM7128 CPLD芯片构成,完成的主要功能有:

(1)将DSP通用I/O引脚信号XFl、XF0扩展为I2C总线所需的SCL、SDA信号,完成DSP对SAA7113的初始化设置;

(2)产生ADV202的片选信号CS和复位信号RESET,将DSP的读写信号R/W扩展为ADV202的读信号RD及写信号WE;

(3)产生DSP外扩存储器SRAM和FLASH的接口信号:地址译码选通信号CE、写脉冲信号WE、读信号OE等;

(4)产生USBN9602的接口信号:片选信号CS、读信号RD、写信号WR、地址引脚信号A0。

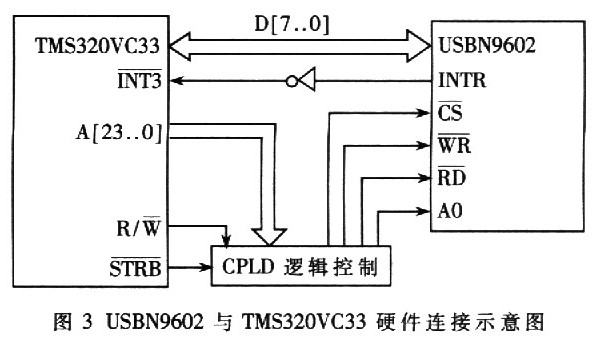

2.4 USB接口设计

USBN9602是美国国家半导体公司推出的一款专用USB接口芯片,支持USBl.1标准。内部具有较大的FIFO.可以缓存大量数据,从而减轻处理器的负担。在本系统中,USBN9602通过并行接口与TMS320VC33相连,接口信号由CPLD控制.工作于非总线复用模式(MODE0=O,MODEl=0),连接示意图如图3所示。USBN9602操作时序是先往地址寄存器中写入地址,然后通过数据输入寄存器和数据输出寄存器读写数据,而地址寄存器和数据寄存器的选择则是通过AO实现的。

2.5 时钟信号的设计

本系统选用3片晶振,其中24.576MHz晶振提供SAA7113所需的外部时钟,LLC产生的 27MHz时钟输出信号提供给ADV202编码芯片使用;5V供电的。15MHz晶振提供给CPLD,并经过CPLD间接提供给DSP使用。从而解决 了不同电平之间的匹配问题,DSP内部锁相环使用×5模式(CLKMDO=CLKMDl=1),工作主频为75MHz;48MHz晶振提供 USBN9602所需的输入时钟。在电路板设计中,时钟信号应尽可能接近相应输入引脚。

2.6 电源及系统复位电路的设计

本系统需要四种电源供电:5V、3.3V、1.8V和1.5V。其中,5V由系统外部电源提供,3.3V、1.8V和1.5V由TI公司的电源芯片TPS767D301通过5V变换提供。TPS767D301可将5V的电源输入转换为3.3V的固定电源输出和1.5~5.5V的可变电源输出,同时产生CPLD的复位信号。

3 视频压缩系统软件设计

3.1 系统软件流程殛总体设计

本系统的软件设计主要分为DSP初始化程序(dspinit.c)、I2C器件SAA7113初始化程序(iic.c)、ADV202初始化程序(init202.c)、 DSP主控制程序(dspetl.c)以及uSB通讯软件的设计。些程序全部在DSP上完成。用C语言开发DSP程序可以缩短开发周期,提高程序开发的效率,也可以使程序的可读性、可移植性大大提高,并且能为系统的改进和升级换代带来极大的便利;对于C语言编写的代码,采用优化编译器生成高效率的汇编代码,可提高程序的运行速度,减少目标代码的度。故在系统软件的总体设计上,采取了以上方法。系统软件流程图如图4所示。

3.2 主要程序实现举例

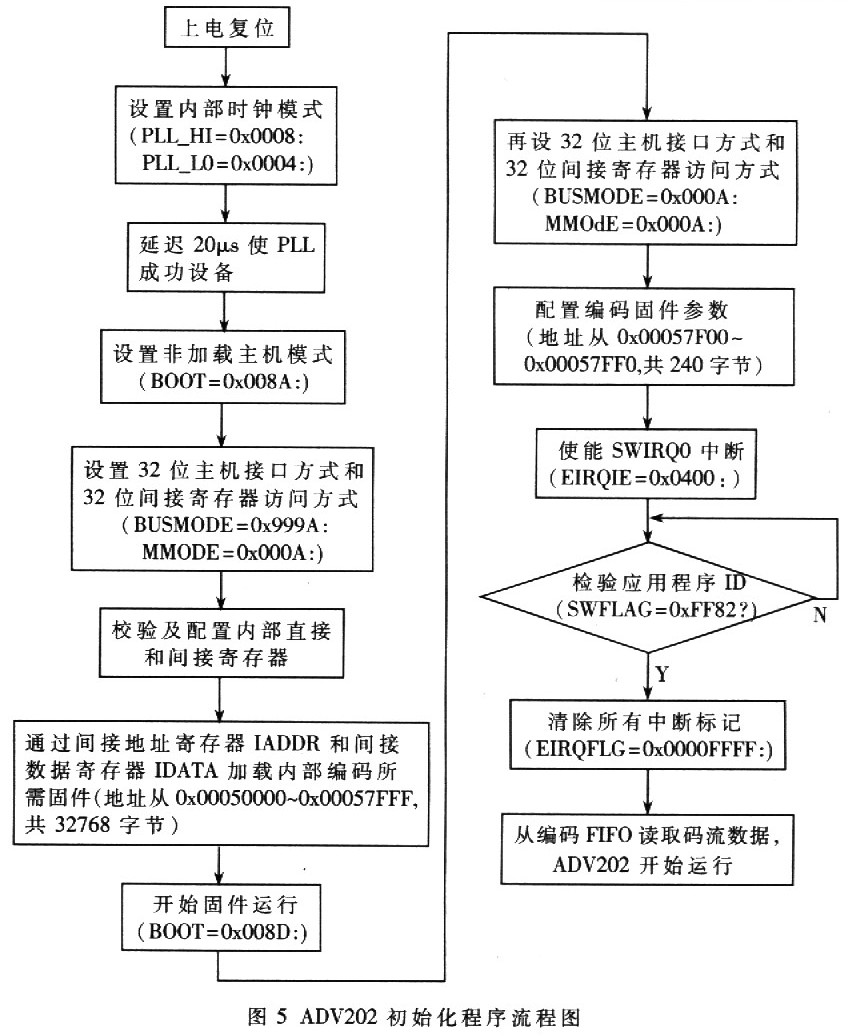

ADV202初始化程序(init202.c)主要完成以下功能:

(1)校验和配置ADV202内部直接寄存器和间接寄存器;

(2)加载编码模式下ADV202所需的固件程序;

(3)对固件配置寄存器进行配置,设置其工作状态;

(4)检验应用程序ID;

(5)清除中断标记,使ADV202进入运行状态。

ADV202初始化流程图如图5所示。

本系统具有体积小、实时性好、压缩信号易恢复等优点,可以广泛应用于非线性编辑系统、远程闭路监视系统、视频信号采集系统、图像和视频档案系统、高质量视频会议系统等。随着ADV202的广泛应用,JPEG2000技术必将成为业界图像视频压缩的主流技术之一。