嵌入式短程无线通信工程系统硬件设计

时间:07-30 10:42 阅读:1590次

*温馨提示:点击图片可以放大观看高清大图

简介:在医疗、工业、智能建筑、消费电子等领域,短程无线通信工程设备设备应用日益广泛,并呈现强的增长势头。本文较为详细地从元器件选择、原理图设计、 PCB板设计、接口吸系统传输距离等方面介绍嵌入式短程无线通信工程系统硬件设计。

引言 在短程无线通信工程系统中,常见的有基于802.11的无线局域网WLAN、蓝牙(blueTooth)、HomeRF及欧洲的HiperLAN(高性能无线局域网)。但其硬件设计、接口方式、通信协议及软件堆栈复杂,需专门的开发系统,开发成本高、周期长,最终产品成本也高。因此,这些技术在嵌入式系统中并未得到广泛应用相反,普通RF产品就不存在这些问题,加之短距离无线数据传输技术成熟,功能简单、携带方便,使得其在嵌入式短程无线产品中得到广泛应用,如医疗、工业、智能建筑、消费电子等领域。这些产品一般均工作在无执照(Unlicensed)无线接入频段,如出一辙15/433/868 /915MHz频段。本文讨论的嵌入式短程无线通信系统,一般包括无线射频RF前端、微控制器(MCU)、I/O接口电路及其它外围设备等。 1 元器件选择 (1)微控制器的选择 嵌入式系统选择处理器时主要需要考虑以下几个方面:处理器性能,所支持的开发工具,所支持的操作系统,过去的开发经验,处理器成本、功耗、代码兼容性及算法复杂性等。 (2) 射频芯片的选择

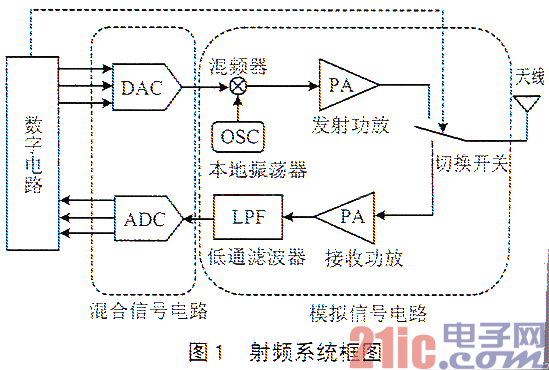

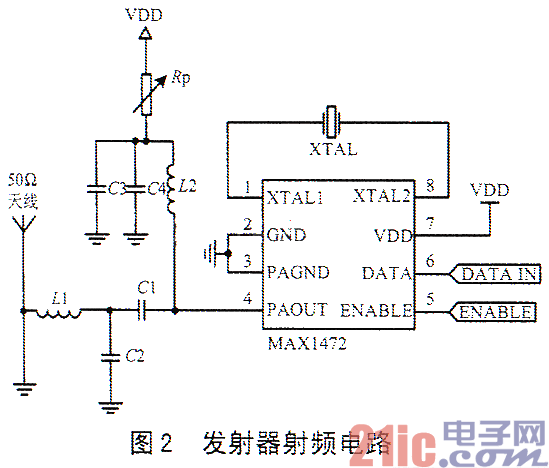

通常,射频芯片的功能框图如图形卡所示。随着无线技术的发展,无线收发芯片的集成度、性能都大幅度提供,芯片性能也各有特色。因而,无线收发芯片的选择在设计中是至关重要的。正确的选择可以减小开发难度、缩短开发周期、降低成本、更快地将产品推向市场。目前,生产此类芯片的厂家主要有Nordic、 XEMICS、Chipcon、TI、Maxim等。选择无线收发芯片时,应考虑以下几个因素:功耗、发射功率、接收灵敏度、传输速度、从待机模式到工作模式的唤醒时间、收发芯片所需的外围元件数量、芯片成本等;同时还须注意当地的无线电管理规定。 (3) 分立元件的选择 所有的RF芯片制造商都在努力提高芯片的集成度但仍然有一些元件很难或者根本无法集成到芯片中去。常将这些分立元件安放在芯片外部,如晶振、PLL环路滤波器、VCO的电感等。在射频电路中,电磁波的波长已可以与分立元件的尺寸相比拟,普通应用于DC和低频集总参数系统的基尔霍夫类型的电流、电压定律已不再适用,须考虑这些分立元件的高频特性及其分布参数。因此,在详细设计时,应多参考所选用芯片资料及相关元件的数据手册。 2 系统原理图设计 嵌入式短程无线通信系统硬件的关键在于其射频电路。这里采用Maxim公司的MAX1472和MAX1473芯片进行射频电路设计。图2是发射器射频电路,图3是接收器射频电路。 MAX1472是一微型3mm%26;#215;3mm的引脚SOT-23封装的VHF/UHF基于锁相环ASK发射机。当工作电压降至2.1V的脱离节锂电池工作,待机模式时仅耗电100nA。在发射过程中,MAX1472发射功率为-10dBm~+10dBm。工作电压3.3V;发射功率+10dbm 时,工作电流仅9.1mA。最高数据速率达100kbps。 MAX1473是一个300~450MHz,采用28引脚,SSOP封装的超外差ASK接收机;具有-114dBm的高灵敏度,高于50dB的用户可选择中心频率镜像抑制并可选择3.3V或5V电源工作电压。在关断模式下电流低于1.5mA,接收时电流为5.2mA;数据速率达100kbps;从关断模式到有效数据输出的过渡时间小于250μs 。 MAX1473包含一个一级自动增益控制(AGC)电路,在射频输入信号功率大于-57dBm时,可降低低哭声放大器(LNA)35dB的增益。接收机使用带有接收信号强度指示(RSSI)的10.7MHz中频滤波器,内置片上集成的锁相环与VCO、基带数据恢复电路。 在原理图设计时,为提高系统的灵敏度,要特别注意天线、低哭声放大器(LNA)和晶振的适配,如图3中标有1、2、3的三处。

3 PCB板设计 高频信号很容易由于幅射而产生干扰,导致振铃(ringing)、反射(reflection)串扰(crosstalk)等;而RF电路对此又特别敏感,因此在PCB板设计时,必须加以重视。为此电源设计时,应在条件许可下采用多层板,提供专用的电源层和地线层。如采用电源总线方式,应尽可能地加粗电源线和地线;尽量减少板上的通孔(包括插件元件的引脚、过孔等);多增加一些地线;分开模拟电源与数字电源;隔离敏感元件;在信号线边上可放置电源线,以最小化信号环路面积,减少环路数量。传输互布线应尽量满足以下规则:避免传输线阻抗不连续(阻抗不连续点是传输先突变点,如直拐角、过孔等,它将产生信号的反射。为此,布线时应避免走线的直拐角,可采用45%26;#176;角或弧线走线,尽可能地少用孔);不要用桩线。其次,要减少串扰。串扰是信号间产生的耦合,分容性串扰和感性串扰两种,通常感性串扰远大于容性串扰。串扰可通过一些简单的办法抑制:①由于容性串扰和感性串扰的大小随负载阻抗的增大而增大,所以应对串扰引起的干扰敏感信号进行适当的端接。②增大信号线间的距离,以减小容性串扰。③为减小容性串扰,可在相邻信号线间插入1根地线;但须注意,此地线每1/4波长要接入线层。④对感性串扰,应尽量减小环路面积,如允许,应消除次环路。⑤避免信号共用回路。最后,随着电路速度的提高,电磁干扰(EMI)越发严重,还须减小EMI。减小EMI的途径通常有:屏蔽、滤波、消除电流环路和尽量降低器件速度。滤波通常有三种选择:去耦电容、EMI滤波器、磁性元件。最常见的是去耦电容,去耦电容用于电源线路滤波。通常在电源接入电路板处放置一个1μF~10μF的去耦电容,以滤除低频噪声;在板上每个源器件的电源引脚处放置0.01μF~0.1μF的去耦电容,以滤除高频噪声。对去耦电容,要注意其放置位置。 4 RF芯片与MCU接口 通过RF芯片实现数据传输。接收端MCU采集RF芯片输出信号通常有三种办法:重复采样(over sampling)、脉冲边沿检测(edge detection)、使用MCU的通用串行通信口(UART)。 重复采样时,用一个三倍于比特率的速率对RF芯片输出信号复复采样,采用采样加权表。对噪音有抑制作用的,适合适应于距离要求较长、可靠性要求较高的场合;但时序要求严格,软件实现时较为复杂。RF芯片与MCU接口可采用MCU的输入输出口。 脉冲边沿检测使用数字信号脉冲实现同步,用RF芯片输出信号作为MCU的中断请求信号。中断程序计算每一比特的采样时间,可处理各种速率的数据流;但每比特仅采样一次,对噪音较敏感,实现算法比重复采样方式更复杂。RF芯片与MCU接口可采用MCU的中断系统及输入输出口。 为简化设计,可使用MCU的通用串行通信接口(UART)。UART对噪声较敏感,但可在软件设计中加以解决,因此通常采用这种接口形式。 5 系统传输距离 (1) 无线通信距离计算 这里给出自由空间传播时的无线通信距离的计算方法。所谓自由空间传播系指天线周围为无限大真空时的电波传播,是理想传播条件。电波在自由空间传播时,其能量既不会被障碍物所吸收,也不会产生反射或散射。通信距离与发射功率、接收灵敏度和工作频率有关。 自由空间下电波传播的损耗: Los=32.44+20lgd+20lgf Los—传播损耗,单位dB;d—距离,单位km;f—工作频率,单位MHz。 如一个工作频率为433。92MHz,发射功率为+10dBm(10mW),接收灵敏度为-105dBm的系统在自由空间的传播距离:①由发射功率+10dBm,接收灵敏度为-105dBm,得Los=115dB。②由Los、f计算得出d=31km。 这是理想状况下的传输距离,实际应用中会低于该值。这是因为无线通信要受到各种外界因素的影响,如大气、阻挡物、多径等造成的损耗。将上述损耗的参考值计入上式中,即可计算出近似通信距离。假定大气、遮挡等造成的损耗为25dB,可以计算得出通信距离为:d=1.7km。 图3 (2) 增加无线通信距离 在工作频率固定的情况下,影响通信距离的主要因素有:发射功率、接收/发射天线增益、传播损耗、接收机灵敏度等。对设计者而言,有的因素是无法选择、改变的,如传播损耗、多径损耗、路径损耗、周围环境吸收等;而有的因素是设计者可以控制的,如发射功率、接收/发射天线增益、接收机灵敏度等。通过调整这些因素,可增加无线通信系统的传输距离。为增加传输距离,设计者常会想到增加发射功率。但增加发射功率会带来一些不利因素。如:由于功率放大器的转换效率低,增加发射功率会大大增加系统的功耗,这对嵌入式系统来说是很不利的;加大发射功率会产生较大的谐波干扰和噪声,并对通信信道产生其它影响,有时反而会影响通信距离。因此,在嵌入式系统中并不提倡采用增加发射功率的办法来增加传输距离。增加传输距离的比较好的办法是,增加接收/发射天线增益一般是选用高增益天线。采用高增益天线具有集成天线、体积小、成本低,实现简单,无需增加额外功耗和元器件等优点。 结语 对一完整的无线系统而言,还有天线设计、MCU及外围电路设计等。此外,由于射频链路的可靠性、误码率(BER,Bit Error Rate)等都比常规有线系统高几个数量级,因此,嵌入式短程无线通信系统一定要加强系统测试,特别是系统误码率(BER)的测试。要把赞成过多误码的背景哭声点找出来,提高系统的性能。限于篇幅,本文不过夜此类问题。