二维条码是为了克服一维条码容量小、信赖数据库的存在、不能表示汉字等缺点而产生的。二维条形码系统是非网络环境下的高安全性信息载体系统,可同步储存照片、虹膜、指纹等生物信息及文字、声音、图像等大量内容,是实现大容量高可靠性信息存储、携带、自动识别的理想系统。现在应用最为广泛的二维条码是美国SYMBOL公司发明的PDF417码,PDF417码是二位条码的美国标准和欧盟标准。我国也已经制定了PDF417码的国家标准GB/T17172——1997。二维条码较磁卡、IC卡的一个明显优势就是成本极低,可在PVC或纸卡上制作,成本几角钱。另外,二维信用条码使用寿命是磁卡、IC卡的十倍。

一个PDF417码最多可容纳1850个字符或1108字节的二晕制数据或2710个数字,其结构见图1。每行从左到右分别为左空白区、起始符、左行指示符号字符、1~30个数据符号字符、右行指示符号字符、终止符、右空白区。

二维条码的一个很重要的特点是可以引入加密机制,信息一旦生成便不可修改。当建立了自己的编译码系统时,就可以在编码过程中加入各种加密形式。比如在二维条形码表面加上水印,在译码时采用同一个水印解密的方法就可以实现条码信息的加密与防伪。在这里,数字水印就是基于二维条码进行信息隐藏的技术。可以利用变形技术对PDF417码符号字符中的各组成单元宽度加以适量的变动,采用误差累积的方式实现隐藏信息的嵌入和提取。由于二维条码使用广泛、体积小、容量大而且人眼无法分辨,因此在二维条码加入水印还有不易引起察觉、携带方便、安全性高、抵御打印扫描攻击、隐藏信息量大等优点。

我国乃至全球都在大力推行二维条码技术。随着二维条码技术的普及,对二维条码识别系统的需求日益增加。在信息安全、现代物流、现代制造、电子商务、电子政务等领域,二维条码识读系统都会有良好的应用1便携式二维条码识读系统的总体设计

本系统要求在FPGA片内利用SoPC技术实现便携式的二维条码识读。它不信赖后台数据库的支持,通过对二维条码的扫描即可将得到的大容量的承载信息(包括文字、头像、指纹等个人信息)在LCD上显示,并可通过USB接口将信息拷贝,或通过RS-232接口将信息上传给PC机,也可以通过GPRS将获得的信息方便快捷地发往数据中心作验证。

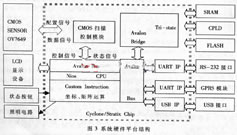

本系统使用集成在QuartusII中的SoPCBuilder开发组件配置生成片上系统。SoPCBuilder是一个功能强大的基于图形界面的片上可编程系统的定制工具,可以在短时间内完成用户定制的SoPC设计。根据应用的需要,应从SoPCBuilder库中选择IP模块、存储器、外围接口和处理器,并且配置生成一个高集成度的SoPC系统。因而选取以下一些IP模块组成片上系统:Nios32bitCPU、BootMonitorROM、CommunicationUARTA、DebuggingUART、Timer、UserPIO、LCDPIO、ExternalRAMBus、ExternalFlashInterface。SoPCBuilder能自动产生每个模块的HDL文件,同时自动产生一些必要的仲裁逻辑来协调AvalonBus上各功能模块的工作。

系统以Altera公司的用于可编程逻辑器件的第二代软核处理器NiosII为核心。NiosII是基于哈佛结构的32位RISC通用嵌入式处理器软核,能与用户逻辑相结合,适配到Altera公司的FPGA中。性能超过200DMIPS。它特别为SoPC设计了一套综合解决方案。本系统采用NiosII的经济型(NiosII/e)。片上系统方式能实现主功能,使系统集成度高、高等性强。

系统结构大体分为三层,由低到高分别为系统硬件层、操作系统层、应用软件层,如图2所示。

最底层的系统硬件层是系统的物理设备基础,提供操作系统和应用软件的运行平台和通信接口。系统的硬件平台在Altera公司的NiosIICyclone嵌入式系统开发板上实现。

第二层的操作系统采用μClinux。这一层提供任务调度以及设备驱动。同时提供中断来实现系统对外界的通信请求的实时响应,如对条码扫描的控制、对GPRS通信端口的控制等。使用操作系统可以提高系统的运行效率和可靠性。

最上层实现条码译码核心算法。该算法能对采集到的条码图像进行高效的处理和匹配,实现译码。这部分工作采用C语言在NiosII的集成开发环境(IDE)中实现。2系统硬件的设计与实现

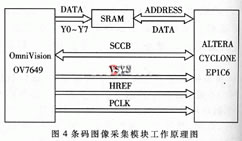

CMOS图像传感芯片为光电转换元件,用于采集二维条码图像,直接输出为数字信号。由外部扩展SRAM存储该数据,再送到Nios进行图像处理。当一组二维条码信息的识别完成时,服务程序控制I/O接口给出中断申请信号,Nios响应此中断申请,进入中断服务程序。译码后的二维条码数据被送入LCD进行显示。动态采集到的二维条码图像存储在SRAM内,而软件程序和PDF417码本都储存在FPGA芯片外扩的FLASH内。

系统硬件电路主要包括以下七个部分:条码图像采集模块、Nios主控模块、GPRS无线通信模块、存储器扩展(FLASH、SRAM、CPLD)模块、输出接口(RS-232、USB模块、照明控制模块。其硬件平台结构见图3。

2.1条码图像采集模块

条码扫描器芯片采用OmniVisionOV7649黑白图像传感芯片,该芯片分辨率为640×480像素,成像速度为30帧/秒,采取逐行扫描方式,输出为数字信号。条码图像采集的程序流程是:首先Nios初始化OV7649的各个寄存器,主要包括状态寄存器(STA)、数据和时钟控制寄存器(CLKRC)和自动增益控制寄存器(AGC)的设置;然后查询等待,条码图像被OV7649采集进入数据寄存器后,通过DMA方式存入SRAM。Nios再从SRAM中提取数据进行译码。这一部分的工作原理见图4。

2.2Nios主控模块

Nios软核CPU实现主要的控制功能。当OV7649准备采集条码图像数据时,Nios发出一个初始信号,控制SRAM重新分配地址块,同时OV7649开始采集条码图像数据。采集完数据并送到SRAM中存储后,Nios开始调用译码程序对图像进行译码。译码完成后,Nios控制条码信息在LCD中显示。

2.3存储器扩展模块

该模块包括FLASH、SRAM、CPLD三个部分。其中,CPLD用于存储配置FPGA的程序,FLASH用于存储系统软件,而SRAM用于存放动态采集到的大量条码图像数据。按照量化位数的不同,选用不同容量的SRAM作为外部扩展,这里选择了IDT71V016,它的容量是64K×16Bit。

3系统软件的设计与实现

这里不采用现有条码扫描大多采用的直接用模拟电路探测条码的条空分界信号的方法,因为这种方法扫描结果将使条空分界线钝化,降低了以后操作中信号检测的准确性。而是将条码图形通过内置CMOS扫描仪整个读取,然后通过嵌入式编程完成条空分界。这种方法的译码准确率要高,而且采用编程的方法不会有前者存在的对扫描角度要求严格的问题。

二维条码扫描器开始工作时,首先采集二维条码图像数据。由于实际工作中条码图像会出现污损等情况,所以必须对采集到的图像进行降噪、校正等处理。条码图像为灰度图像,必须对其进行二值化处理才能进行码字识别。在将PDF417码的所有码字正确分割后,还要以查表方式在码本中查找与码字相对应的值。为确认扫描的有效性,还要进行校验。如出错,则进行纠错。最后,传输译码的数据到LCD显示。条码图像译码算法的流程如图5所示。

译码流程说明如下:

·降噪处理

这里采用多帧图像平均降噪方法。图像采集芯片OV7649成像速度为30帧/秒,为消除在实际操作过程中由于人手抖动、条码图像移动等而产生的误差,每一次扫描只取六帧图像,所有时间为0.2s,可以忽略抖动的影响。

·背景分离

背景分离是将条码区与背景分离,从而避免在没有有效信息的区域进行特征提取,加速后续处理的速度。背景分离采用标准差阈值跟踪法实现,图像条码部分由黑白相间的条块组成,灰度变化大,因而标准差较大;而背景部分灰度分布较为平坦,标准差较小。将条码图像分块,每个小块的标准差若大于某一阈值。则该小块中的像素点为有效;否则为背景。

·图像校正

由于扫描进来的图像总会出现一定的倾斜和偏移,给快速、正确地识别条码带来困难。利用行差运算与Hough变换相结合的方法,能快速、准确地找到检测二维条码图像边界线,估计出倾斜角度,从而对图像进行矫正。

·图像二值化

通过统计整个条码的边界强度,得出图像的边界强度直方图。直方图中边界强度较小的部分对应着噪声边界,边界强度较大的部分对应着条码的条、空边界。由于边界强度直方图具有明显的双峰结构,可以采用基于阈值选取的方法寻找最佳阈值。因为每次的光照等外界条件是不同的,此二值化门限电平必须是动态调整的。根据这个阈值分离出噪声边界和条、空边界。

·码字识别

在码字割完成之后,要把数据码字转换成PDF417码的符号字符。首先检测起始符位置,然后开始分割码字,每17个模块就确定为一个码字,直到检测完所有码字,码字分割即完成。这一过程可以通过采用模板匹配方式在固定的码本中查找与码字相对应的值来实现。也就是利用Query语句查询数据库查出相应的PDF417符号字符。·信号纠错

PDF417码在识读过程中,由于条码图案的损坏,或扫描数据传输出错,会出现袱发错误。Reed_Solomon错误控制码适合纠正突发错误,一般情况下使用R-S错误控制码对码字进行检错和纠错。但在有严重污损的情况下,R-S码已经不能达到要求。可以利用简单的堆积式二维条形码图像处理算法——“边缘规整”算法,虽然不能从根本上解决污染的清除问题,但可以大大降低译码错误率。

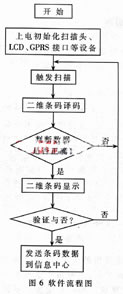

整个系统软件部分大致分为设备初始化、条码图像采集、译码、条码内容显示、数据输出等几部分。软件流程图见图6。

4自定义指令的应用

在条码识别算法中,对条码图像的处理,数据运算量大,循环数目多。如在对条码图像校正的过程中,需要频繁地用到坐标转换。为了达到系统的实时性要求,对于算法的硬件加速是必不可少的。采用Nios处理器的定制指令,把用户自定义的功能直接添加到Nios的ALU中去,用一组易于通过硬件实现的位移和加法运算替代乘加运算,完成坐标的转换和许多循环的数据处理,加快专项任务的执行。用户逻辑和用户指令是NiosII系统最闪亮的特点之一。同时,充分利用了可编程逻辑器件硬件执行运算速度快的优点,这一点和用于控制NiosCPU的特点相得益彰。定制指令逻辑的NiosII的连接在SoPCBuilder中完成。NiosII配置向导提供了一个可添加256条定制指令的图形用户界面,在该界面中导入设计文件,设置定制指令名,并分配定制指令所需的CPU时钟周期数目。系统生成时,NiosIIIDE为每条用户指令产生一个在系统头文件中定义的宏,可以在C应用程序中像调用函数一样方便地直接调用这个宏。

本文提出了一种基于NiosII嵌入式软核处理器的便携式二维条码识别系统的实现方法。使用Altera公司的CycloneFPGA实现,具有开发周期短、成本低等特点;同时采用NiosII的定制指令提高系统性能,利用硬件执行运算速度快的优点,使以NiosII处理器为核心的系统能够快速地完成大量数据的处理。随着二维条码越来越广泛的应用,此方案会有更广阔的前景。