经过近几年的快速发展,嵌入式系统(Embedded System)已经成为电子信息产业中最具增长力的一个分支。随着手机、PDA,GPS、机顶盒等新兴产品的大量应用,嵌入式系统的市场正在以每年30%的速度递增(IDC预测),嵌入式系统的设计也成为软硬件工程师越来越关心的话题。

在嵌入式系统设计中,低功耗设计(Low Power Design)是许多设计人员必须面对的问题。其原因在于嵌入式系统被广泛应用于便携式和移动性较强的产品中,而这些产品不是一直都有充足的电源供应,往往是靠电池来供电的;而且大多数嵌入式设备都有体积和质量的约束。另外,系统部件产生的热量和功耗成比例,为解决散热问题而采取的冷却措施进一步增加了系统的功耗。为了得到最好的结果,降低系统的功耗具有下面的优点:

(1)电池驱动的需要。在强调绿色环保时期,许多电子产品都采用电池供电。对于电池供电系统,延长电池寿命,降低用户更换电池的周期,提高系统性能与降低系统开销,甚至能起到保护环境的作用。

(2)安全的需要。在现场总线领域,本安问题是一个重要话题。例如FF的本安设备,理论上每个网段可以容纳32个设备,而实际应用中考虑到目前的功耗水平,每个网段安装10个比较合适。因此降低系统功耗是实现本安要求的一个重要途径。

(3)解决电磁干扰。系统功耗越低,电磁辐射能量越小,对其他设备造成的干扰也越小。如果所有的电子产品都能设计成低功耗,那么电磁兼容性设计会变得容易。

(4)节能的需要。特别是对电池供电系统,功耗与电压的平方成正比即:P=V2/fC+Pstatic,因此节能更为重要。

1 功耗产生的原因

1.1 集成电路的功耗

目前的集成电路工艺主要有TTL和CMOS两大类,无论哪种工艺。只要电路中有电流通过.就会产生功耗。通常,集成电路的功耗主要有4个:

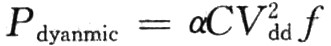

(1)开关功耗。对电路中的电容充放电而形成,其表达式为:

式中:Vdd为电源电压;C为被充放电的电容:α为活动因子;f为开关频率。

(2)静态功耗和动态功耗。当电路的状态没有进行翻转(保持高电平或低电平)时,电路的功耗属于静态功耗,其大小等于电路电压与流过电流的乘积;动态功耗是电路翻转时产生的功耗,由于电路翻转时存在跳变沿,在电路翻转瞬间,电流比较大.存在较大的动态功耗。目前大多数电路都采用CMOS工艺,静态功耗很小,可以忽略。起主要作用的是动态功耗,因此从降低动态功耗人手来降低功耗。

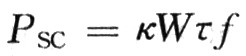

(3)短路功耗。因开关时由电源到地形成的通路造成的,其表达式为:

式中:κ由工艺和电压决定;W为晶体管宽度;τ为输入信号上升/下降的时间;f为工作频率。

(4)漏电功耗。由亚阈值电流和反向偏压电流造成。目前大多数电路都采用CMOS工艺。故漏电功耗很小,可以忽略。

1.2 电阻的功耗和有源器件的功耗

通常为负载器件和寄生元件产生的功耗。有源开关器件在状态转换时,电流和电压比较大,将引起功率消耗。另外,CMOS电路中最大的功耗来自于内部和外部的电容充放电产生的功耗。

2 硬件低功耗设计

2.1 选择低功耗的器件

选择低功耗的电子器件可以从根本上降低整个硬件系统的功耗。目前的半导体工艺主要有TTL工艺和CMOS工艺,CMOS工艺具有很低的功耗,在电路设计上尽量选用,使用CMOS系列电路时,其不用的输入端不要悬空,因为悬空的输入端可能存在感应信号,它将造成高低电平的转换。转换器件的功耗很大,尽量采用输出为高的原则。

嵌入式处理器是嵌入式系统的硬件核心,消耗大量的功率,因此设计时选用低功耗的处理器;另外,选择低功耗的通信收发器(对于通信应用系统)、低功耗的访存部件、低功耗的外围电路,目前许多通信收发器都设计成节省功耗方式,这样的器件优先采用。

2.2 选用低功耗的电路形式

完成同样的功能,电路的实现形式有多种。例如,可以利用分立元件、小规模集成电路,大规模集成电路甚至单片实现。通常,使用的元器件数量越少,系统的功耗越低。因此,尽量使用集成度高的器件,以减少电路中使用元件的个数,减少整机的功耗。

2.3 单电源、低电压供电

一些模拟电路如运算放大器等。供电方式有正负电源和单电源两种。双电源供电可以提供对地输出的信号。高电源电压的优点是可以提供大的动态范围,缺点是功耗大。例如,低功耗集成运算放大器LM324,单电源电压工作范围为5~30 V。当电源电压为15 V时,功耗约为220 mw;当电源电压为10 V时,功耗约为90 mw;当电源电压为5 V时,功耗约为15 mw。可见,低电压供电对降低器件功耗的作用十分明显。因此,处理小信号的电路可以降低供电电压。

2.4 分区/分时供电技术

一个嵌入式系统的所有组成部分并非时刻在工作,基于此,可采用分时/分区的供电技术。原理是利用“开关”控制电源供电单元,在某一部分电路处于休眠状态时,关闭其供电电源,仅保留工作部分的电源。

2.5 I/O引脚供电

嵌入式处理器的输出引脚在输出高电平时,可以提供约20 mA的电流,该引脚可以直接作为某些电路的供电电源使用,如图2所示。处理器的引脚输出高电平时,外部器件工作;输出低电平时,外部器件停止工作。需要注意。该电路需满足下列要求:外部器件的功耗较低,低于处理器I/O引脚的高电平输出电流;外部器件的供电电压范围较宽。

2.6 电源管理单元设计

处理器全速工作时,功耗最大;待机状态时,功耗比较小。常见的待机方式有两种:空闲方式(Idle)和掉电方式(Shut Down)。其中,Idle方式可以通过中断的发生退出,中断可以由外部事件供给。掉电方式指的是处理器停止,连中断也不响应,因此需要进入复位才能退出掉电方式。

为了降低系统的功耗,一旦CPU处于“空转”,可以使之进入Idle状态,降低功耗;期间如果发生了外部事件,可以通过事件产生中断信号,使CPU进入运行状态。对于Shut Down状态,只能用复位信号唤醒CPU。

2.7 智能电源设计

既要保证系统具有良好的性能,又能兼顾功耗问题,一个最好的办法是采用智能电源。在系统中增加适当的智能预测、检测,根据需要对系统采取不同的供电方式,以求系统的功耗最低。许多膝上型电脑的电源管理采用智能电源,以笔记本电脑为例,在电源管理方面,Intel公司采取Speed Step技术;AMD公司采取Power Now技术;Transmeta公司采取Long Run技术。虽然这三种技术涉及到的具体内容不同,但基本原理是一致的。以采用Speed Step技术的笔记本电脑为例,系统可以根据不同的使用环境对CPU的运行速度进行合理调整。如果系统使用外接电源,CPU将按照正常的主频率及电压运行;当检测到系统为电池供电时,软件将自动切换CPU的主频率及电压至较低状态运行。

2.8 降低处理器的时钟频率

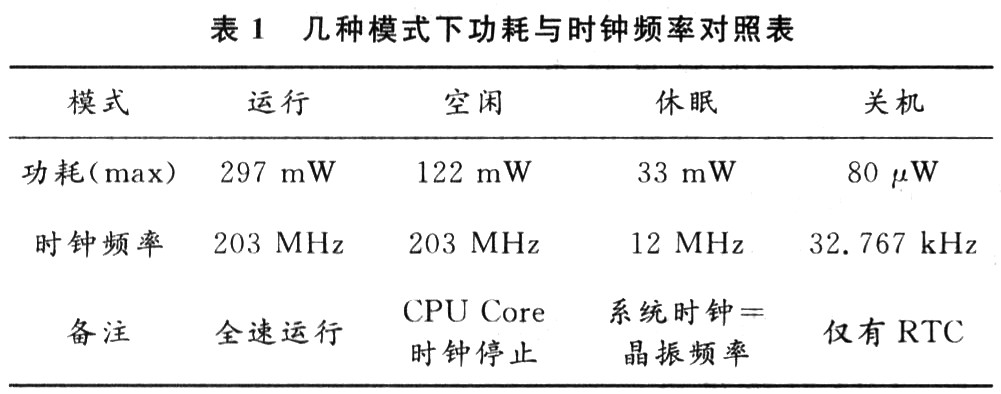

处理器的功耗与时钟频率密切相关。以SAM-SUNG S3C2410x(32 b ARM 920T内核)为例,它提供了四种工作模式:正常模式、空闲模式、休眠模式、关机模式.各种模式的功耗如表1所示。

由表1可见,CPU在全速运行的时候比在空闲或者休眠的时候消耗的功率大得多。省电的原则就是让正常运行模式远比空闲、休眠模式少占用时间。在类似PDA 的设备中,系统在全速运行的时候远比空闲的时候少,所以可以通过设置,使CPU尽可能工作在空闲状态,然后通过相应的中断唤醒CPU,恢复到正常工作模式,处理响应的事件,然后再进入空闲模式。因此设计系统时,如果处理能力许可,可尽量降低处理器的时钟频率。

另外,可以动态改变处理器的时钟,以降低系统的总功耗。CPU空闲时,降低时钟频率;处于工作状态时,提高时钟频率以全速运行处理事务,实现这一技术的方法。通过将I/O引脚设定为输出高电平,加入电阻R1,将增加时钟频率;将I/O引脚输出低电平,去掉电阻R1,可降低时钟频率,以降低功耗。

2.9 降低持续工作电流

在一些系统中,尽量使系统在状态转换时消耗电流,在维持工作时期不消耗电流。例如。IC卡水表、煤气表、静态电能表等,在打开和关闭开关时给相应的机构上电,开关开和关状态通过机械机构或磁场机制保持开关的状态,而不通过电流保持,可以进一步降低电能的消耗。

3 软件低功耗设计

3.1 编译低功耗优化技术

编译技术降低系统功耗是基于这样的事实:对于实现同样的功能,不同的软件算法,消耗的时间不同,使用的指令不同,因而消耗的功率也不同。对于使用高级语言,由于是面向问题设计的,很难控制低功耗。但是,如果利用汇编语言开发系统(如对于小型的嵌入式系统开发),可以有意识地选择消耗时间短的指令和设计消耗功率小的算法来降低系统的功耗。

3.2 硬件软件化与软件硬件化

通常的硬件电路一定消耗功率,基于此,可以减少系统的硬件电路,把数据处理功能用软件实现,如许多仪表中用到的对数放大电路、抗干扰电路,测量系统中用软件滤波代替硬件滤波器等。

需要考虑,软件处理需要时间,处理器也需要消耗功率,特别是在处理大量数据的时候,需要高性能的处理器,这可能会消耗大量的功率。因此,系统中某一功能用软件实现,还是用硬件实现,需要综合计算后进行设计。

3.3 采用快速算法

数字信号处理中的运算,采用如FFT和快速卷积等,可以大量节省运算时间,从而减少功耗;在精度允许的情况下,使用简单函数代替复杂函数作近似,也是减少功耗的一种方法。

3.4 软件设计采用中断驱动技术

整个系统软件设计成处理多个事件,在系统上电初始化时,主程序只进行系统的初始化,包括寄存器、外部设备等,初始化完成后,进入低功耗状态,然后CPU控制的设备都接到中断输入端上。当外设发生了一个事件,产生中断信号,使CPU退出节电状态,进入事件处理,事件处理完成后,继续进入节电状态。

3.5 延时程序设计

延时程序的设计有两种方法:软件延时和硬件定时器延时。为了降低功耗,尽量使用硬件定时器延时,一方面提高程序的效率,另一方面降低功耗。原因为:大多数嵌入式处理器在进入待机模式时,CPU停止工作,定时器可正常工作,定时器的功耗可以很低,所以处理器调用延时程序时,进入待机方式,定时器开始计时,时间一到,则唤醒CPU。这样一方面CPU停止工作,降低了功耗,另一方面提高了CPU的运行效率。

4 结 语

嵌入式系统的设计涉及到软件设计和硬件设计两个方面,在实际系统应用时,低功耗的设计并非是一蹴而就的事情,需要综合考虑各种可能的因素、条件和状态,需要对各种细节进行认真的斟酌和分析,需要对各种可能的方案和方法进行计算和分析,这样才可能取得较为满意的效果,达到降低系统功耗的目的。