理解、测量和优化时钟分发的附加抖动性能

时间:09-28 11:14 阅读:3088次

*温馨提示:点击图片可以放大观看高清大图

简介:在高速通信应用中,系统设计人员需要在平衡性能和成本预算的同时优化时钟性能。当选择最佳时钟时,开发人员必须考虑多种影响因素

在高速通信应用中,系统设计人员需要在平衡性能和成本预算的同时优化时钟性能。当选择最佳时钟时,开发人员必须考虑多种影响因素,例如性能、成本、尺寸和输出逻辑等,从事频域工作的人员更关注相位噪声;而从事时域工作的人员则更关注抖动性能。例如在PC机主板设计中,优选的时钟信号通常需要分发到多个逻辑输入或位置,大量工作被用于优化时钟性能。当判定系统总体性能时,时钟缓冲器将成为等式中的组成部分,而同时对相位噪声和抖动的影响因素也将成为等式中的组成部分。为了满足设计规格要求,在通过制造商发布的数据手册比较和选择各种时钟特性时,理解如何测量时钟缓冲器的相位噪声,什么能影响时钟缓冲器的性能,什么细节必须考虑对工程师而言是很重要的。

时钟分发IC不直接生成时钟信号而是再生并提供多个时钟拷贝。因此,时钟分发IC的相位噪声只能在有输入信号时进行测量。衡量时钟分发IC质量最常用的术语是“附加相位噪声”,而经常不被提及的是附加相位抖动的标准测量方法。在这里,我们采用Silicon Labs的Si53311时钟缓冲器来展示表征附加相位抖动的一种推荐方法,以及影响缓冲器性能的各种因素。相同的原则和测试方法能够用于分析大多数缓冲器、分频器和其它分发IC的性能。重要的是理解附加抖动性能与下列可变因素的相关性:

1 在给定幅度下的输入信号上升和下降时间,或者转换速率

2 输出格式

3 输出频率

4 电源电压

输入信号上升和下降时间显著影响附加相位抖动。虽然,乍一看,这是真的,但是使等式更完整的是考虑上升和下降时间以及幅度,或者更好的是幅度与上升下降时间的比率,可以表示为V/ns,或转换速率。大多数工程师仅将转换速率与模拟器件相关联,例如运算放大器,在数字器件数据手册中转换速率并不常见。虽然转换速率并不常见,但它是描述附加相位噪声改善或衰减更准确的方式。如果转换速率值没有给出,那么可以根据数据手册中的技术参数计算出来。举例来说,假设有一个差分LVDS信号,它具有350mV的单端振幅和400ps的上升和下降时间。测量点在20%和80%时,差分转换速率将是(2×350mV×0.6)/(400ps)或1.05V/ns。(出于我们的论述目的,这里我们使用差分转换速率)。

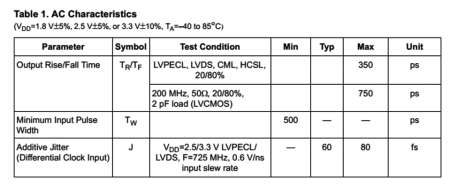

同样,相位噪声只能在有输入信号的情况下进行测量,而且应该测量总体抖动。时钟缓冲器的影响被称为“附加相位抖动”。表1显示了一个附加相位抖动规格示例,需要注意的是测试条件包括转换速率、输出频率、逻辑电平格式和工作电压,所有这些都会影响附加抖动。当进行附加抖动性能比较时,为了使对比有意义,必须使用相同的测量条件。如果没有使用相同的测量条件,那么可能得到不正确的结果,在最坏的情况下,如果系统设计者期望满足一个规格,但时钟缓冲器的工作条件不佳,将不能达到要求。

表1 附加相位抖动规格