摘要:众核技术已成为当前处理器体系结构发展的必然趋势,如何对众核处理器设计进行有效而充分的验证,成为当今IC 设计验证领域的研究热点之一,也是众核处理器芯片能否成功流片的关键因素之一。目前工业界采用基于仿真的验证作为主要的验证方式,本文重点介绍了以覆盖率为导向的RISC 众核处理器的功能验证环境的整体设计,提出了“被动式”的验证思想,并采用“软硬件协同验证”的策略,最终达到每条指令都比对通过的验证目标,辅以后期阶段所引入的时序验证策略和功耗评估策略,完整地提出了一套芯片验证平台搭建和验证功能实现的方法流程。

1 引言

在随着集成电路制造工艺的进步和处理器设计水平的不断提高,众核技术已成为当前处理器体系结构发展的必然趋势。处理器的复杂度呈指数幅度上升,使故障的查找和修复变得越来越困难,如何对众核处理器进行有效而充分的验证,成为当今IC 设计验证领域的研究热点之一,也是其能否能最终流片成功的决定性因素。传统的功能验证方法主要采用监测并控制其地址与数据总线的方法,这对于高度集成化的众核芯片,其追踪系统总线的策略往往不能定位内部故障所在,从而不能进行下一步的分析和修改故障。

基于软件和硬件分别进行独立的仿真验证仍然是目前IC 验证主要应用的功能验证方式,在此基础上,本文重点介绍了以覆盖率为功能验证导向的RISC 众核处理器的验证环境的整体搭建,提出了“被动式”的测试验证思路,并采用“软硬件协同验证”的策略,最终达到了处理器运行的每条指令都对比通过的验证目标。再辅以相应基于成熟EDA 工具的功耗和时序分析验证方式,完整地提出了一套芯片验证平台搭建和验证功能实现的方法流程。

文章共分为以下几个部分:第2 部分描述在“被动式验证”思想的指导下RISC 众核处理器验证环境的搭建;第3 部分详细描述为了达到“单条指令对比”效果的众核处理器的验证策略和具体实现;第4 部分为结束语,作为本文总结。

2 众核处理器验证环境的搭建

2.1 软硬件协同验证的发展现状

软硬件协同验证与传统的数字系统仿真验证方法不同,它是针对软件和硬件系统模块进行的混合模拟仿真。传统的系统验证方法通常是将软件部分和硬件部分的设计验证分开独立进行,二者在确定了设计目标之后就很少再相互考虑。这样的设计验证方法在系统设计后期才会发现比如软硬件接口或在设计初期没有考虑到的系统功能方面的问题,导致设计资源的浪费与设计周期的延长和开发成本的不断增加。

软硬件协同验证技术的出现很好地改善了这一现状,它分为外围硬件模型验证和处理器核心验证两个部分。软硬件协同验证通常使用硬件模拟器作为验证工具,通过执行RTL 级设计描述模拟设计的物理实现,其仿真结果取决于设计描述是否正确反映了设计的物理实现,验证时需要通过测试平台产生激励和开发人员检查响应的有效性。

2.2 RISC 众核处理器概述

本文选取一款名为“Godson-T”的RISC 架构处理器芯片为研究对象和载体。该款芯片是由中国科学院计算技术研究所系统结构国家重点实验室设计的一款片上众核处理器芯片,主要面向电信应用。服务器。金融管理。医疗和大型数据库系统等领域的高性能计算。该款众核处理器目前已经顺利通过各项验证和测试,并成功Tape-out.

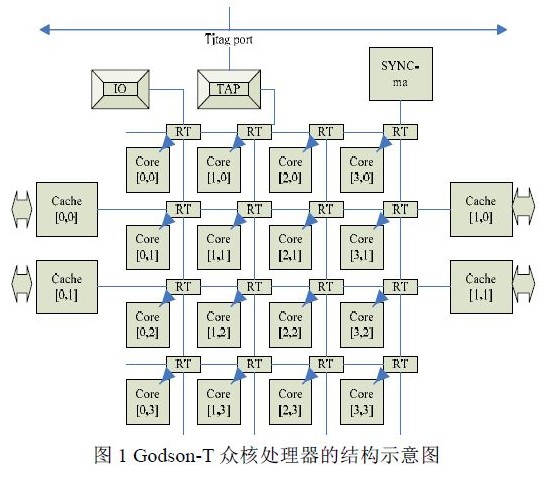

该款众核处理器的结构如图1 所示,中间部分为四纵四横的十六单元阵列,每个单元由一个处理器小核和一个RT 组成,两边各有两个L2–Cache,为二级数据缓存,为十六个独立小核共享。

在示意图的上方,SYNC-ma 模块(同步管理器)负责同步管理各独立小核间的互联与协调。

TAP 端口负责与JTAG 调试相关的接口进行通信的模块,IO 模块负责向片外发送相关配置信息。

2.3 验证语言System Verilog 概述

SystemVerilog 简称为SV 验证语言,是IEEE1364 Verilog-2001 标准的扩展增强,兼容VerilogHDL 2001,并已经成为硬件设计下一代验证仿真的主流编辑语言。SV 语言结合了来自VerilogHDL.C 语言。面向对象设计语言的部分概念,另外包含了Assertion 语言和平台语言,完美结合了验证过程中使用频繁的高层验证性语言(HVL)和开发过程中使用较多的硬件描述性语言(HDL),对于进行当今高度愈加复杂的设计验证工作无疑是提供了一种有效的解决思路。它具有接口(interface)。断言(Assertion)。多线程(multiplethreads)和函数和任务(Function and Task)等多种新的验证平台建模技术。

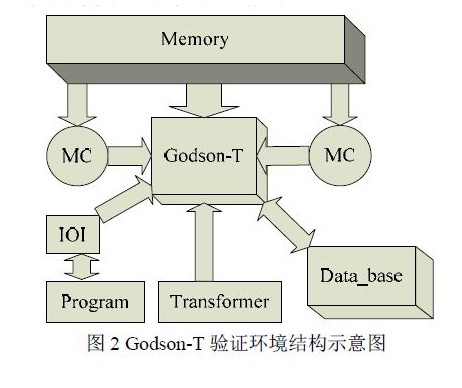

2.4 验证环境的整体设计Godson-T 整体验证环境设计主要由六部分组成。包含处理器小核在内的其顶层实现模块作为待测硬件部分,参考验证模型模拟器Transformer作为测试软件部分,这两部分具体体现软硬件协同验证的策略;内存空间Memory 由一段C 代码负责维护和执行相关操作,容量为4GB.输入输出接口模块(IOI)负责进行接口配置;两个同构的Memory Controller 模块(MC)分置两侧,用来针对和控制访存操作;一个存放着在验证过程中可能出现故障信息的数据库Data_base 和若干具有分选功能的选择器等共同组成验证环境中的附属模块。其结构示意图如图2 所示。

在 Godson-T 被动式验证的指导思想下,验证环境必须做到主动去适应和满足测试小核的对每个测试程序的执行操作和处理动作,而让待测小核能够在不受平台外部条件任何干扰和容错性相关的影响下自主完成自身设计功能体现。

验证环境中由C 代码负责维护的内存空间只识别可执行文件,故在初始化时,程序列表中等待测试的程序需首先进行编译,再进行加载。向内存中加载可执行文件是通过调用加载函数实现的,该加载函数的功能是从程序列表按照一定次序依次中读取测试程序,直到所有测试程序都加载完毕。

编号为 core[0,0]作为测试程序的主核,既是需要测试的小核之一,也是测试环境中负责向其余小核客户传递消息的起点。所有测试程序依次轮训每个小核首先需要将消息发送至core[0,0],待测目标小核收到与之相匹配的调试编号开始进行取指。访存等操作,这样目标小核在调试状态下就进入了运行过程。如果是同时测试多个小核对与多线程程序运行的情况,主核会根据需求创建出多个线程,并通过片上网络进行资源调用和分配,使各个小核相继运行自身的线程任务,这样就实现了众核处理器测试环境地初步搭建。

完成了验证环境搭建的首要工作。具体的验证策略细节会在下一章进行详细的介绍。