1 引言

可编程控制器(Programmable Logic Controller)具有抗干扰强、可靠性高、编程简单的特点,被广泛应用于工业控制领域。但是传统小型可编程控制器难以将智能控制算法嵌入到控制系统中。本文以嵌入式微处理器S3C44B0X+FPGA为核心设计通用小型的可编程控制器,论述了PLC主机各功能模块通过CAN总线与S3C44B0X连接的接口电路和主机程序设计及执行过程。通过FPGA配置I/O口和嵌入先进的智能控制算法,如PID、模糊控制、神经网络算法等,这些控制算法作为控制模块嵌入PLC的梯形图程序中作为功能模块调用,各个模块之间通过CAN总线连接,用户根据被控对象现场的需求可以选择多个人机界面装置,提供监控控制系统运行状态的便利。

2 PLC系统的总体设计

系统采用32位嵌入式微处理器S3C44B0X作为可编程控制器的CPU,以此为核心扩展系统需要的存储器;通过FPGA扩展PLC所需要的I/O口,完成相应输入输出模块的设计;系统通过微处理器的SPI接口扩展CAN总线,用于连接上位机、主控机、编程器、以及液晶显示与触摸屏等功能模块进行通信,用户根据被控对象现场需求可以选择多个人机界面装置,这些装置作为扩展模块挂接在CAN总线上;实现智能控制算法的FPGA与主机微处理器S3C44B0X的I/O口连接。用户使用手持编程器编写指令表程序后,通过CAN总线传输到控制主机的存储器中,以便CPU执行这些程序;系统运行的状态参数通过CAN总线传输到监控系统中,在监控系统中显示系统运行的状态;FPGA实现的智能控制算法作为控制模块嵌入PLC梯形图程序中作为功能模块调用。系统的结构框图如图1所示:

图1 系统结构框图

3 PLC主控器的设计

3.1系统存储器的扩展

3.1.1 存储器Nor Flash 的扩展

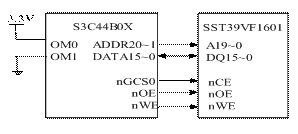

可编程控制器需要掉电保存系统启动的引导程序、梯形图或指令表程序,以及解释梯形图或指令表的解释程序,而S3C44B0X微处理器内部没有存储器。闪速存储器(Flash Memory)具有非易失性,并且可轻易擦写,在嵌入式系统中得到广泛的应用。所以本课题采用了2MB的SST39VF1601存储器来存储上面提到的引导程序、解释程序及用户程序。该存储器采用标准的总线接口与处理器交互,对它的读取不需要任何特殊的代码。由于系统启动的引导程序储存在Flash ROM,要把其映射在处理器的Bank0地址空间,这样系统上电复位后,处理器就自动从0x00000000地址处开始取得指令运行。Flash与S3C44B0X的接口电路图如图2所示。处理器ADDR20~1对应着Flash ROM的A19~0,偏移了1位,这是由于S3C44B0X是按照字节编址的,而Flash ROM是以16位为一个存储单元。

图2 程序存储器Nor Flash的扩展

3.1.2 SDRAM 的扩展

随机存取存储器RAM(Random Access Memory)是易失性的存储器,在掉电后数据即消失。但与ROM器件不同的是,它的随机读写速度非常快,写入数据之前也不需要进行擦写,这些特性使它成为嵌入式系统中必不可少的存储设备之一。为了提高系统执行的速度,在系统启动时,把梯形图或指令表程序复制到读写更快的RAM中,这样系统执行程序的过程在RAM中完成,提高了可编程控制器扫描程序的周期。

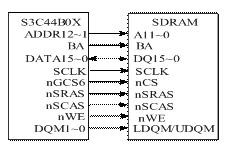

常用的RAM分为SRAM和DRAM两种类型,其中DRAM又分为DRAM和SDRAM。S3C44B0X芯片本身提供了与DRAM与SDRAM直接接口的解决方案,因此只需对与存储器控制器相关的寄存器进行的适当的配置。本系统采用的同步动态存储器SDRAM为8MB的HY57V641620,映射在Bank6地址空间。接口电路图如3所示。这里的BA即A22~21。由于HY57V641620的存储结构为:1Mbⅹ16ⅹ4 Bank,在电路上以A22~21作为bank地址选择线。

图3 SDRAM的扩展

3.1.3 EEPROM的扩展

在可编程控制器中,一些编程软元件的数据内容需要掉电保存,如:D数据存储器、部分特殊辅助继电器M等。系统通过S3C44B0X自带的IIC接口扩展EEPROM,用来保存这些掉电需要保存数据的编程软元件,在系统启动时,首先把这些软元件的值从EEPROM拷贝到SDRAM中,以便提高系统执行速度。采用的EEPROM型号为:AT24C512,系统扩展原理图如下。系统扩展只需要两根线,一根数据线,一根时钟线,这两根线加上拉电阻是因为IIC总线是开漏输出。

图4 IIC接口扩展EEPROM

3.2 I/O口扩展

在嵌入式微处理器S3C44B0X中总共有71个普通的I/O口,这些I/O引脚大多都是多功能引脚,其中一些I/O口已经作为专门的应用。系统实现的目标需要128个I/O口,即可编程控制器具备128个点,这样微处理器本身的I/O口无法满足系统的需要,需要通过FPGA扩展。

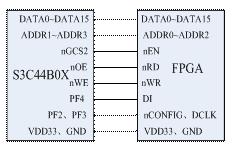

采用的FPGA型号为EP1K30TC208-3。该芯片具有208个引脚,可配置的I/O口最多达到147个。系统通过S3C44B0X总线进行扩展,这样操作FPGA的I/O口就像操作ARM本身的I/O口一样,操作起来非常的方便。FPGA与S3C44B0X的连接框图如图5:

图5 FPGA配置I/O口

ARM地址线、数据线与FPGA的地址线、数据线连接,由于FPGA每个存储单元是16位,而ARM微处理器每次处理的是8位,因此地址线要偏离一位;FPGA的存储单元映射到ARM中的Bank2;nOE、nWE分别是读写信号线;TxD0用来下载FPGA工作需要的配置文件;PF2、PF3、TxD0共三根线提供FPGA启动工作需要的时序;SCLK是ARM与FPGA工作(读、写)需要的时钟.

3.3 输入输出模块的扩展

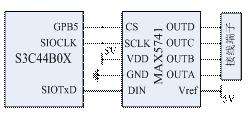

可编程控制器输入输出模块主要有数字量和模拟量输入输出。模拟量的输入输出即A/D、D/A是对象过程参数和PLC主机之间的接口。对象过程参数经过传感器转换成标准的电量后,经过A/D转换器进入PLC主机中;PLC主机经过D/A数模转换把数字量转换成模拟量输出。由于S3C44B0X微处理器内部带有了8路10位的A/D转换器,在一些要求不是很高的控制领域,该转换器可以满足要求,因此不需扩展。S3C44B0X内部没有D/A转换器,所以采用的D/A转换器为MAX5741进行扩展,该转换器是4路10位,使用SPI接口进行扩展,其与微处理器的连接原理图如图6:

图6 D/A转换器的扩展

3.4 CAN总线扩展

系统使用CAN现场总线在各个模块之间交换数据、通信,如:用户使用手持编程器或PC机编写梯形图或指令表程序后,通过CAN总线把程序传输到PLC主机中。由于微处理器S3C44B0X本身没集成CAN控制器,需要单独扩展CAN控制器,采用的CAN控制器为MCP2510,收发器为PCA82C250。MCP2510工作电压为3.3V,能够直接与S3C44B0X微处理器I/O口相连。为进一步提高系统抗干扰性,可在CAN控制器和收发器之间加光耦隔离6N137,原理图如图7:

图7 CAN总线的扩展

4 程序设计及执行过程

程序设计一个关键技术是编写梯形图或指令表程序的解释程序。根据指令的逻辑关系,分别给每条指令编写其对应的子程序,当CPU扫描到某条指令的编码时,就调用其子程序,进行逻辑运算,并把结果送到映像寄存器中。

程序执行过程分为三个阶段:输入处理阶段、程序执行阶段、输出处理阶段。如图8所示。系统上电后,完成堆栈、存储器、中断等的初始化;把D数据寄存器值、部分M特殊辅助寄存器值等一些需要掉电保持的数据,从EEPROM拷贝到SDRAM指定的地址中;把用户编写的梯形图或指令表程序从Nor Flash拷贝到SDRAM中以便提高系统的运行速度。最后系统才真正开始扫描用户编写的梯形图或指令表程序。

图8 程序执行过程

在输入处理阶段,CPU读取所有输入端子的状态,并把这些状态内容保存在输入映像寄存器中;在程序执行阶段,CPU根据输入状态的信息,从梯形图或指令表程序的第一步开始执行,当CPU扫描到有关智能控制模块时,把智能控制模块的一些设置值、参数送到FPGA中, FPGA在主机扫描程序的同时,并行处理智能控制算法,并不断的把运算的结果送到控制参数存储器中;在输出处理阶段,把输出映像寄存器中的内容送到输出锁存寄存器中,使输出端口电平发生变化,执行机构动作驱动要控制的对象,最后把指针指向程序的第一步,使程序周而复始的工作,直到收到停止工作信号为止。

5 结论

本文创新点:基于CAN现场总线、嵌入式微处理器S3C44B0X+FPGA设计的可编程控制器,采用了32位集成度高的嵌入式微处理器S3C44B0X为核心,简化了电路的设计,提高了系统的可靠性及运行速度;通过FPGA配置I/O口,解决了众多芯片I/O口不足的问题,满足了工业控制领域的需求。同时在FPGA中实现的智能控制算法作为功能模块嵌入PLC梯形图程序中,主机执行程序的同时,FPGA也在并行完成智能控制算法的运算,即不影响系统执行的速度,又解决了传统小型PLC不能嵌入智能算法的问题。