PART 1:

1. 软件 14.1版本较 13.6版本功能提升了,bug也减少了,但是还是存在一些 bug,功能方面还有待进一步完善。

(Cadence在每个季度都会发布软件补丁程序QSR,用户可以在Sourcelink网站注册并预定QSR光盘,您会在一周内直接收到该光盘;在这期间,Cadence还会根据实际情况,不断发布最新的临时升级、补丁程序,Cadence当地的技术支持人员会主动、尽快地为用户进行安装。在功能方面,Cadence在世界各地拥有强大的研发队伍,以向客户提供更多、更好的功能。PSD14.2版本很快将交付用户,功能更强的PSD15.0不久也将发布。)

2. cadence 公司目前在华东地区现只有 1名技术支持,在现场技术支持方面有待加强力量。

(Cadence今年在中国正式注册成立了全资公司,服务队伍也从去年的30人增加到近90人,并在上海、北京成立了High Speed Technical Centre等部门,在各地包括华东地区都增加了技术支持,因此我们相信,在新的一年里,我们的客户会得到更多更方便的支持)

3. 随着 cadence 软件在公司的日益推广使用,我们希望能加强软件使用方面的培训力度。

(感谢贵公司对Cadence公司的支持!如果贵公司有软件培训方面的需求,可直接和当地的客户经理联系。)

PART 2:

CADENCE BUG 主要有:

1. 在CONCEPT HDL 中移动器件,会出现器件库可以被分拆。

(这个问题是14.0中出现的BUG,14.1版已解决此问题。请各位升级)

2. 从CONCEPT HDL 打包时经常在没有报出错误的情况下,不能打包成功.

(Concept HDL打包不成功时一定会报错。这种情况可能是因为路径错误,请仔细检查)

3. 从CONCEPT HDL 打包到ALLEGRO更新PCB时不能打包成功. 但往空的PCB打包时能成功, ECO常有问题.

(在个别情况下,会出现这种情况,出错信息为“Net name already exists”。今年2月份的补丁盘已包含此补丁程序,请用户联系Cadence工程师进行升级或到下面地址下载补丁程序、安装:

ftp://ftp.cadence.com/patches/PSD141/allegro/algroF2B14.10-s018wint.exe

ftp://ftp.cadence.com/patches/PSD141/allegro/algroBase14.10-s056wint.exe)

4. CCT 中有时不能单独对电源、地 FANOUT。

(是否没有指定Power Nets选项?如果指定了还有此问题,用户最好能提供一个可以重复出现此问题的例子,以便查找原因)

5. BOARDQUEST 对网络拓扑的提取常常不能成功。 不如以前的版本灵活、方便,在模型有“问题”时,可以用缺省模型。

(Boardquest 为Cadence较早版本。用户最好能提供一个可以重复出现此问题的例子,以便查找原因)

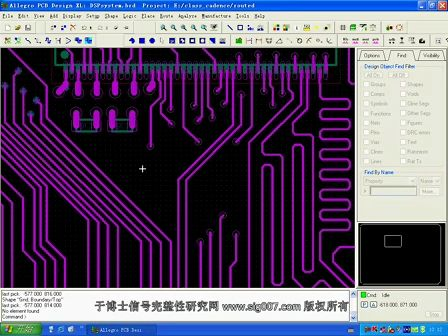

6. ALLEGRO 中大面积布铜时,有时会出现在对铜皮分配了网络的情况下,布出死铜(铜皮不与任何网络相连,无花盘). 大面积布铜时,经常出现不应该有的裂缝,布铜的效果不是最优的。

(用户最好能提供一个可以重复出现此问题的例子,以便查找原因)

7. ALLEGRO 中程序自动、无告警退出, 致使设计丢失的现象,发生的频率比以前的版本高。

(出现这种情况,主要是操作系统方面的原因,ALLEGRO要求在英文NT或WINDOWS 2000下使用.在中文WINDOWS 2000下,出错概略提高许多。事实上,设计人员应充分使用Allegro的Autosave功能,以避免各种情况下引起的数据丢失)

8. ALLEGRO出光绘时,常报出根本不存在的错误而不能输出光绘文件。

(根据经验,此类问题一般是TOP,BOTTOM层光绘有问题。最好能提供一个可以重复出现此问题的例子及系统给出的错误信息,以便查找原因。)

9. ALLEGRO 的功能还有改善的空间。如: 修线时,自动采用原线宽; 替换功能、推挤功能、加测试点功能可以做得更加友好,等等。

(即将发布的14.2版本对这些大部分问题做了很多改进。下面列出14.2版的一些主要改进:

Save Design to 14.0

Database Write Locks

View Schemes

DBdoctor

Plane Rat

Place Manual UI Auto-Hide

Direct Select of Alternate Symbol

Quickplace Options

Via Shoving

Dynamic Slide Phase II

Vertex Dynamic Bubble Options

Smart Start on Line Width

Highlight All Pins on Net During add connect

Cadence Design Systems, Inc

Net Name Added to Control Panel

Purge Vias

EXTRACT Name Change

Graphical Enhancements During Dynamics

Text Printing/Stick

Append to File Option Added to Reports

SPECCTRA-Like Zoom

Viewer Plus Enhancements

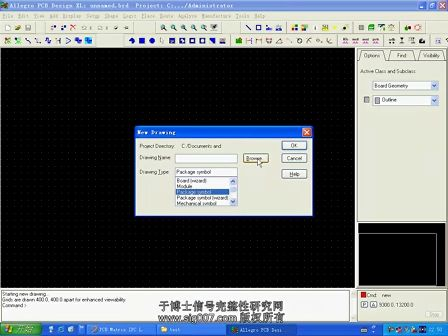

New Board Wizard

CPM and CDS_SITE Support

Scald EOL

IPC356 and Allegro-to-DXF Performance Improvement

TestPrep PCR Fixes

New Features in Allegro Studio (PCB)

Miscellaneous Category)

10. 生成料单时,有PPT 表的元器件的 Part Name 在料单中出现两次。

(14.1版已解决此问题)

PART 3:

我们在使用CADENCE的过程中遇到的问题基本归结为:

1 无论哪个版本都经常出现自动退出,提示为非法操作,然后不能存盘,自动退出。(ALLEGRO)

(参考PART2问题7的答案。提示:Allegro在异常退出时,会在当前设计目录下产生一个后缀为sav的文件。用Allegro打开该文件,另存为brd文件即可)

2 版本13.6中出现过生成的GERBER文件在避让不能的SHAPE时,出现半圆,即不能完全避让。还出现过个别完全不避让的状况 。

(题目意思不太清楚。请使用最新版本测试)

3 版本14.1很多机器不能正常安装。

(请参考软件安装手册,并注意安装过程中系统给出的提示。一般出现这种问题都是操作系统问题或放火墙、防病毒软件引起)

4 在添加IBIS模型时,MPC8260总是不能自动加上去,已经和工程师联系过多次。

(可能是因为该IBIS模型不是标准格式,请使用器件商提供的标准模型)

PART 4:

1在ALLEGRO中,编辑焊盘时,经常会出现“执行程序错误”而退出程序,且没有备份文件,导致之前的工作白费。

(此问题14.1已经解决,而且同样与操作系统有关)

2 在从自动布线器(SPECCTRA)建军回到ALLEGRO后,输出表层的线、孔就与器件成为一个整体,移动器件时,线、孔就附在上面一起移动。

(实际上,这个功能是Cadence应大多数用户要求而添加上的,主要是为了方便移动器件的时候 fanout 后的引腿和 via 能跟着一起移动。如果你实在不愿意这么做,可以执行下面这个Skill程序解决,以后版本将会有选项供用户选择:

; The following Skill routine will remove invisible

; properties from CLINES and VIAS.

; The intent of this Skill program is to provide

; users with the ability of deleting the invisible

; properties that SPECCTRA/SPIF puts on. This will allow the moving

; of symbols without the attached clines/vias once the

; design is returned from SPECCTRA if the fanouts were originally

; put in during an Allegro session.

;

; To install: Copy del_cline_prop.il to any directory defined

; within your setSkillPath in your

; allegro.ilinit. Add a "load("del_cline_prop.il")"

; statement to your allegro.ilinit.

;

; To execute: Within the Allegro editor type "dprop" or

; "del cline props". This routine should

; only take seconds to complete.

;

; Deficiencies: This routine does not allow for Window or

; Group selection.

;

; WARRANTIES: NONE. THIS PROGRAM WAS WRITTEN AS "SHAREWARE" AND IS AVAILABLE AS IS

; AND MAY NOT WORK AS ADVERTISED IN ALL ENVIRONMENTS. THERE IS NO

; SUPPORT FOR THIS PROGRAM.

;

; Delete invisible cline/via properties.

;

axlCmdRegister( "dprop" 'delete_cline_prop)

axlCmdRegister( "del cline props" 'delete_cline_prop)

(defun delete_cline_prop ()

;; Set the Find Filter to Select only clines

(axlSetFindFilter ?enabled (list "CLINES" "VIAS")

?onButtons (list "CLINES" "VIAS"))

;; Select all clines

(axlClearSelSet)

(axlAddSelectAll) ;select all clines and vias

(setq clineSet (axlGetSelSet))

(axlDBDeleteProp clineSet "SYMBOL_ETCH") ;Remove the property

(axlClearSelSet) ;unselect everything

)

3 建原理图软件中,图形编辑和SYMBOLS中的设置不一致,SYMBOLS中的任何设置变动都会使图形的编辑无效。

(问题表达不太清楚,请直接联系支持工程师)

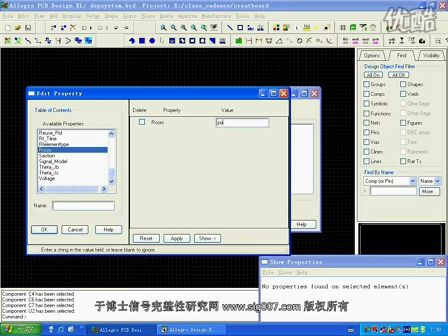

4 建库中,在一个器件对应三个或以上的封装时,PACKAGE中所建的三个封装在SYMBOLS中并没有全部出现以供SYMBOLS图形选择。

(不会有这样的问题。问题有些含糊:建库时,在 Part developer 中,对symbol 的设定本来就没有 package 的图形选择;如果是在原理图里添加 Symbol遇到这个问题,如果要选择封装形式,需要用 Physical 方式,请确认操作是否正确,下面就是多个封装同时显示的例子:)

5 原理图建库的PART-TABLE表的属性中COMP-NAME的值与CELL名相同时,不能够封装,封装时出错。

(请提供该元件的库,以便于我们查找原因)

6 原理图库建库属性中,PART-NUMBER 的值不能 NULL,否则向 SPECCTRA 转换时出错。

(的确如此,PART_NUMBER的值不能为空,解决办法:要么删除PART_NUMBER属性,要么把值加上)

7 在 ALLEGRO 中鼠标显示为无穷大是可以的。但在 SIGNOISE 的界面下,设为无穷大时就显示不出来了。

(14.1 版本已解决此问题。对早期版本可以在命令行执行 :set pcb_cursor=infinite 即可;另外,Specctraquest 没有提供象 Allegro 一样的User Reference 功能,可以在命令行执行 enved 调用该功能界面,然后进行设置)

PART 5:

1.用贴片焊盘(type=single)做成的package,用tools\padstack\modify design padstack...编辑,发现type变成了blind/buried。为什么会这样?

(这是软件显示上的小漏洞,但是丝毫不影响使用,焊盘还是事实上的single)

2.修改过焊盘后以同名保存(替换了原来的焊盘),但是用tools\padstack\modify design padstack...检查用该焊盘做的package,发现仍旧是老焊盘,而事实上任何目录中老焊盘都不存在了。既然allegro是要到pad_path中调用焊盘的,为什么会出现这种情况?

(修改完焊盘之后, 需要update pad才能更新,因为Allegro是把相关的数据都纳入到brd文件集中管理的)

3.打开padstack editor就会出现这样的提示:pad_designer:Can't open journal file。于是新做的焊盘无法保存,提示:failed to open file '#T001632.tmp'。

(请检查系统环境变量设置是否正确;另外所有路径都不能使用汉字)

4.AELLGRO中竟然无UNDO、REDO这种常用FUNC,让人非常费解!!!

(15.0版本将增加Undo、Redo功能)PART 6:

1,ALLEGRO中直接从库中调的元件不能定义网络及 Ref des。

(是的。这样一来可以保证你LAYOUT结果和原理图目的是一致的,而不会因为不小心而出错。一般我们不应该直接从库中调元件,而应通过导入新的NETLIST 来增加新元件.)

2,ALLEGRO中只能 UNDO一次,简直不能容忍。

(15.0版本将增多步Undo、Redo功能)

3,公英制转换偏差太大。

(由于计算精度的限制,公英制的来回转换会产生一定的累积误差,因此在设计过程中,应尽量避免频繁转换公英制)

4,Toolbar的功能描述没有。Toolbar 随意添减图标易出错。

(在下面版本中,Allegro将会有Toolbar的功能描述。你可以先选择Defaults,然后部分改变toolbar,但是只要是正常操作,Toolbar 的添减是不会出错的)

5,差分信号线调成圆弧线段很困难。

(可能是靠里面的线半径设的过大了)

6,对于颜色的设置不能EXPORT 颜色文件,每块PCB都必须重新设置颜色。

(Allegro没有保存颜色表的功能,但是可以通过其他简单的方法解决,如:调用Script功能;或着准备一个空板,里面只保存偏好的颜色设置,把网表Export到这个空板就可以了)

8,Allegro里没有对齐元件的功能。

(后面版本的Allegro将会有对齐功能)

9,选择元件或Trace时,不能如 CONCEPT HDL 添加漏选的东西或者不能去除多选的东西,也就是说,在板内划出矩形选择框,框到啥就是啥,框到不想选的东西,那也得承受,没有框到要选择的东西,那也没办法。

(如果选择零散目标的话,可以使用Temp Group功能,例如:Move->右键-> Temp Group->点选->Complete)

10,垃圾文件太多,不知那些有用。

(Cadence 实际上极少产生垃圾文件,许多文件都是设计高速PCB所需要的。每个文件的作用可以参考培训手册)

11,Allegro布线时,相同的网络和Trace为什么不能都高亮显示?

(14.1 以后版本已解决)

12,Allegro步线抓焊盘的功能太弱,不能保证线段结束时连接在PIN的中心。

(在Allegro右面的Control panel->Option中选择:Snap to connect point,并请在布线时连到Pad前,右键选TOGGLE即可。如经常性出现此问题,可将 TOGGLE设成快捷键方式)

13,编辑Shape 时,选择Boundary还得十分小心,有一点重合都不行。

(可以通过调整GRID来修改铜箔,这样一来更容易)

14.CCT 布线时网络不高亮;由 ALLEGRO 到 CCT 前布的线只能删除,不能回退,不能自动优化鼠线.

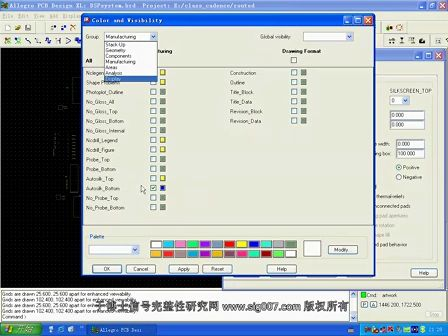

15.ALLEGRO:鼠线不能只显示当前屏幕上的PIN的鼠线,全屏布线时高亮不明显.

(方法一:可以在setup->user preference->display中,勾选display_nohilitefont项,将高亮设为实线显示;

方法二:改变高亮颜色。点击Hilight 按钮,右面控制面板的Option 栏会提供可选择的颜色表;

方法三:使用Shadow Mode,明暗的对比度可以在Color and Visibility中的Shadow Mode 项调整。)

三种方法配合使用,会得到更好的显示效果。

16.在ALLEGRO中,改变线宽时鼠标需放在线宽栏的右边才可改变。

(使用时光标应在Control Panel区域,一旦移到 Work area 就开始执行Allegro命令,因此就不能再进行输入,不过这个问题是可以改进的)

17.放置器件时,不能在原理图里同时选多个元件拖放到PCB里(布局时).

(14.1 就可以。在ConceptHDL 中按住Shift 键多选,然后在Allegro里便可依次放置)

18.布局不能优化网络,飞线以最近连接显示,而不是最佳显示方式(没有动态连接功能)。

(Cadence 注重约束驱动布线,因此不会有飞线的动态连接)

19.在 ALLEGRO 中没有网络也可以走出一根走线.(很容易造成多余的线头)并且清除线头及多余过孔也不彻底!(GLOSS命令)

(如何去掉断线头?分为有网络属性的断线头和VIA,同无网络属性的断线头两种。

对无net 的断线头,可以通过Hilight 来实现,要把Hilight 的Color 同client相区别。可多试几试hilight 的color 来发现断线头。

对有net 属性的断线头和VIA(如图二),可采用:

在 ROUTE/GLOSS/PARAMETER 下,选中 1,2,3 项,点选 GLOSS 即可(如下图):

点击左边的方按钮,还可以改变参数的设定。

20.14.0 的原理图到 14。1 的 PCB 转网表时在空板时可以转入,但是后来网表变化,不能转进来 (报错:NET NAME ALREADY EXIST),有时换一台机器即可,随机性很大!

(此问题已解决,请安装最新的补丁盘或到下面地址下载补丁程序、安装:

ftp://ftp.cadence.com/patches/PSD141/allegro/algroF2B14.10-s018wint.exe

ftp://ftp.cadence.com/patches/PSD141/allegro/algroBase14.10-s056wint.exe)

21.铜箔及差分线倒圆弧非常不方便,没有直接的命令可以在走完90或45度角后,方便倒圆弧(最好能像CADSTAR拉圆弧)

(我们会把此问题报告到Cadence R&D,希望尽快解决)

22.ALLEGRO中最好可以方便走排线。

(CCT 具备此功能。Allegro走排线功能正在开发中)

23.14.0做库,库sym字符在原理图中可以随便移动

(14.1 版本已解决)

24.14.0做库,在14.1原理图中sym旋转,而字符不随着旋转(如:电解电容的“+“号)

(14.1最新的补丁盘已解决此问题)

25 14.0原理图中的sym如果 mirror,转到14.1看元件并未 mirror

(14.1最新的补丁盘已解决此问题)

26.做库时,用HDL 编辑完元件,如果回到 PART DEVELOPMENT 存盘,就会将刚改完的元件回复成未改前的图形。

(即将发布的14.2版本已解决此问题)

27.用Net logic 改变的网络不能反标至原理图

(可以。用tool2->design association可以反标网络)

28.Allegro 关于 area 的规则不能完全带入 CCT,即只能带入 region 规则,不能带入region class 等比region优先级更高的规则

29.14.1 CCT 内有些线在没有对其进行任何操作的情况下,有时候会莫明其妙的变到另一层中 (有时从CCT回到ALLEGRO,会发现本来在 BOTTOM 层的变成 TOP层)

(最好能提供一个可以重复出现此问题的例子,以便查找原因)

30.Allegro 和 CCT 都没有 snap 的功能,即当直线至目标 PIN 附近时,会自动吸附到 PIN 的中心。BGA 布线时,由于 PIN 间允许走线的范围很小,要把鼠标位置定得很精确才能拉出一根线,实际操作很费劲。如果有 snap 功能的话,就可以允许有一定的裕度,如 8mils,即当鼠标左右偏移小于 4mils 且偏移位置不允许布线时,route 应停留得最接近该位置的允许布线区

(Allegro 和CCT都有snap功能)

31.Allegro没有BUS 走线的功能,差分线不能同时布线

(目前走BUS线可以到 CCT里完成。从PSD14.2 开始,Allegro对差分线的处理功能将会大大加强)

32.CCT 差分线布线困难,经常不能转弯,而且有时候想单独处理其中一根线时不被允许

(这种情况可在ALLEGRO中处理,15.0将会对此做较大改进)

33.CCT同时走多根线可差分线时不允许two-seg方式,以不能精确定位

(同上)

34.CCT的two-seg布线方式和Allegro布线时要不断功换toggle 功能,非常不方便,应让软件自动识别。

(同上)

35. 14.1CCT 中鼠标中键的功能经常莫名其妙地丢失

(可在命令行中键入” bind_mouse_button M zoom_pan”来恢复.)

36.布线时设定过孔,无法用预缆方式,只能自己去了解过孔名,然后自己敲名字。

(这的确是一个缺点。该问题已列入15.0改进计划)

37.在allegro里推动过孔时有可能会冒出一大堆错,还不能undo.

(14.2对过孔的推挤有很大改进)

38.有时优化走线时,旧线还需要再手动删除。

(优化走线是在原走线的基础上进行,因此不会有新线产生)

39.电源地线进到cct时容易掉线。

(最好能提供一个可以重复出现此问题的例子,以便查找原因)

40.设定最小线长与最大线长,当线长小于设定时,没有 DRC 报错(ELECTRICAL CONSTRAINT SPREATSHEET)

(在 14.0 版本以后,Allegro 增加了未布线的最小线长检查,可以通过对环境变量CHECK_MIN_DELAYS 的设置来实现,如果设置为 ON的话,当线长小于设定时,将会有DRC报错。其检查的依据是两个PIN之间飞线的曼哈顿距离)

41.13.6做的原理图,转到14.1不能将数据传递给已经UPREV 的原13.6的板.

(问题提的不很清楚。从14.0开始:

1、因为添了约束管理器,不能从高版本的向低版本传递数据;

2、uprev13.6的板时Flash symbol 也需要uprev,勾选use preference中 Misc里面的old_style_flash_symbols 即可;也可以使用批处理转换,DOS命令:

FOR %%f IN (*.bsm) DO flash_convert %%f

3、如果跟约束有关,要注意原来的DELAY_RULE 和MATCHED_DELAY 已改为 PROPAGATION_DELAY 和RELATIVE_PROPAGATION_DELAY)

42. ALLEGRO中UPDATE SYMBOLS 时,LIBRARY中的该元件明明已改过来, 但就是不能UPDATE过来,并且从PACKAGE SYMBOL 中也看不到该器件(不选DATA BASE,就选LIBRARY)

(应该是路径方面的问题,不然 Package Symbol 里不会看不到的,请仔细检查一下环境变量的设置。或者你可以这么试试,在 Concept 里重新以 Phisical方式Add 这个器件,然后Export(用Update Allegro Board 并且勾选 ECO)

附注:如果用户对以上解答内容不理解、经过测试仍未解决问题或还有其他更多的问题,请及时与Cadence当地工程师联系:

畅学电子

畅学电子