在今年1月举办的美国消费电子展(CES)上,数家主要平板电视及显示技术公司纷纷宣布推出高清3D电视和令人惊艳的4kx2kLCD显示器,从而可将用户家中、车内或移动设备上的电视、显示器以及其他电子设备之间需要交换的数据量提升至前所未有的水平。在这些最新的电视上,体育迷们可以欢欣鼓舞地体验到众多优异性能,如176°的超广视界、1200:1的超高对比度以及450尼特的亮度——足以使最阴暗的洞穴通透明亮。

本文引用地址:http://www.eepw.com.cn/article/236289.htm

不过,对于开发这些电视或连接至这些电视的电子产品的设计工程师来说,最新特性需要非常高的带宽。例如,一部具备800万像素的四声道4kx2k高清电视(可为家庭提供数字影院效果)需要的带宽是当前顶级电视和显示器在理想工作状态下的4倍,这意味着在机顶盒与高清电视之间存在巨大的数据吞吐量。

对更高带宽的需求并不单来自消费产品市场,为了满足MRI和CT扫描、命令与控制、菊花链显示、电子公告牌与DNA3D渲染、航空器、天气以及人体构造等众多领域的显示需要,广播设备、数字显示、科研以及医疗市场也在不断加大对带宽的要求。

为了在控制成本的同时还能有助于满足这种带宽需求,视频电子标准协会(VESA)于2007年向市场推出了DisplayPort。如今,VESADisplayPort1.1a已能够在单根线缆内支持多达4个通道且每通道最高2.7Gbit/s的数据率,而DisplayPort1.2又将支持的数据数率翻番,达到5.4Gb/s(足以在单显示器应用中支持3840×2400像素(60Hz),或4台显示器应用中的1920×1200像素,或2560×1600像素的3D显示(120Hz))。DisplayPort可同时支持两种嵌入式显示,如笔记本电脑的显示器,以及视频“源端”设备(机顶盒、DVD播放机、PC图形卡以及笔记本电脑)和独立显示设备(HDMI与DisplayPort标准文档中所称的“宿端”设备)之间的盒至盒连接(box-to-boxconnection)。

而赛灵思(Xilinx)推出了名为XilinxLogiCOREDisplayPortv1.1(v1.2将在IDS12.1中配套提供)的灵活可编程VESADisplayPortv.1.1a解决方案。在用户展开设计之前,建议先了解与该标准的部分关键功能有关的背景信息,如PolicyMaker,以及如何使用Xilinx即将推出的XAPP“使用MicroBlaze嵌入式系统实施DisplayPortSourcePolicyMakerControllerSystem参考设计”在东京电子设备(TED)提供的Spartan-6消费类视频套件上完成实施工作。

PolicyMaker:关键性差异

在显示市场上,VESA通过DisplayPort引领着从VGA、DVI以及HDMI等协议成功升级至高速串行收发器、基于包的层架构协议。与并行协议不同,串行分组协议在实现和维持连接或链路方面要多一层复杂性。在VESADisplayPort1.1a规范中,控制功能被划分为LinkPolicyMaker和StreamPolicyMaker。LinkPolicyMaker可管理链路,并负责保持链路同步。其任务包括发现链路、对链路进行初始化和维护。StreamPolicyMaker可管理传输初始化,并通过底层硬件对行动序列施加控制来维护同步流。

PolicyMaker的上述要素需根据特定的实施来决定,而且可在操作系统、软件驱动程序、固件或者FPGA逻辑中进行配置。为简化使用,许多商用DisplayPortIC将Link和StreamPolicyMaker对设计人员隐藏。若用户显示要求与套装的DisplayPortASSP相匹配,其价格和易用性无可争辩。但是,希望产品在竞争中脱颖而出的设计人员倾向于采用FPGA。

SourcePolicyMaker参考设计

DisplayPortSourcePolicyMakerControllerSystem参考设计采用赛灵思MicroBlaze嵌入式系统来实施与商用套装DisplayPort芯片类似的功能,且具备可进行源代码定制的额外优势。通过使用该参考设计的应用手册,用户不必对PolicyMaker进行详细了解即可顺利启动设计工作,仅需简单地将范例设计连接起来。

除了上述源代码设计之外,DisplayPort的传输(Tx)或源端内核也配套提供了用于实现有限状态机(FSM)控制器的额外范例设计。

在显示市场上,VESA通过DisplayPort引领着从VGA、DVI以及HDMI等协议成功升级至高速串行收发器、基于包的层架构协议。

DisplayPortTxFSM控制器范例设计(顶级文件名dport_tx_fsm_cntrl)配套提供DisplayPortLogiCORE源端设计范例。此概念验证设计内含基于RTL的有限状态机,以实施可演示正确启动流程的简单PolicyMaker。dport_tx_fsm_cntrl设计范例的优势在于可以显著缩短仿真时间。

SourcePolicyMakerControllerSystem参考设计采用MicroBlaze嵌入式系统XAPP,其顶级ISE项目名称为“dport_source_ref_design.xise”。它使用户能够根据自己需要对SourcePolicyMakerController的源代码进行修改。此外,还能够与LogicCOREv1.2(IDS12.1)和Spartan-6TED消费类视频套件协同运行。

上述两种范例设计均包含可实现内核设置及链路和流维护的基本流程。

功能概述

源端、宿端/视频规范都会采用PolicyMaker,但在DisplayPortLogiCORE中,赛灵思对它们进行了差别实施。与源(发送)端的PolicyMaker功能相比,宿(接收)端的PolicyMaker功能要简单得多。赛灵思在LogiCORE内实施了大部分宿端PolicyMaker功能。基于RTL的宿端控制器可提供剩余部分的功能。由于源端PolicyMaker的功能复杂得多,因而可采用源代码参考设计的方式提供。

让我们来深入了解源端PolicyMaker,其使设计人员能够最大限度地提高功能灵活性与实施灵活性。顶级范例设计包含内核的两个高级组件示例:XAPP使用MicroBlaze嵌入式系统实施DisplayPortSourcePolicyMakerControllerSystem参考设计;以及DisplayPort内核源端(发送)设计。赛灵思将内核的实施分成原子链路功能,分别称为主链路、二级通道以及AUX通道协议。主链路可实现主视频流的交付。二级通道可在消隐期内将音频信息的交付集成到主链路中。赛灵思将在未来的内核中提供二级通道。同时,AUX通道可为宿端通信通道建立专用源端(见图2)。

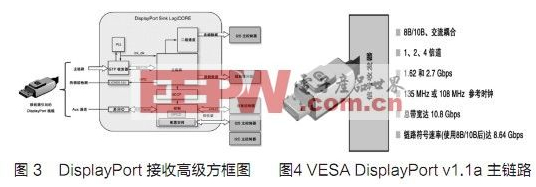

赛灵思为用户数据接口新增了线路缓存器,使用户能够在FPGA(见图2、3和4)中便捷实施范例设计。图3中宿端的PolicyMaker与DeviceController都是COREGeneratorTM所提供宿端设计范例的组成部分。

MicroBlaze处理器发挥核心作用

赛灵思推出的SourcePolicyMakerController可与内核配合使用,这样其功能在很大程度上和ASSPDisplayPort源端设备一样。建议您使用MicroBlaze嵌入式或外部处理器来正确初始化和维持该链路。XAPP包含的PolicyMaker参考设计预配置版本在FPGA内的MicroBlaze处理器中实施,可帮助用户立刻将设计方案转换成硬件。正式供货时的参考设计将包含设计人员可修改的源代码。

SourcePolicyMakerController设计的“逻辑”部分位于MicroBlaze处理器之上,并使用I2C命令来控制链路、数据流以及配置空间。该C语言代码可实施PolicyMaker的指令控制、高级示例文件以及嵌入式开发套件(EDK)。同时赛灵思还提供软件开发套件(SDK)项目文件,可为设计人员最大限度地提高实施灵活性。此外,赛灵思还可为使用现有控制平台处理器的应用提供C语言源代码。设计人员可将该源代码添加至FPGA内外的现有控制软件中。根据许可证协议,只要代码能够同内核配合使用,控制器即可在FPGA外部实施(即在外部处理器中实施)。

设计人员可使用支持赛灵思PlatformStudio(EDK)的嵌入式硬件设计套件或具有SDK的嵌入式软件设计套件,对XAPP设计进行修改。通常情况下,FPGA设计人员使用EDK,而软件开发人员则使用SDK。EDK流会生成一个中间网络文件(NGC),您可以在实施设计之前,将其整合在ISE项目中。NGC文件包含构成BRAM初始化一部分的MicroBlaze代码。

快速转换

如果用户修改过软件,EDK流通常会占用较长的时间。不过,用户一旦生成了网络列表,就不再需要EDK或者SDK了。SDK流可修改FPGA比特流,因此仅需更新BRAM中的MicroBlaze代码内容。该SDK流能够为软件修改提供更快的转换时间,但在这种情况下,用户必须每生成一个比特流就使用一次SDK。

在DisplayPort中,VESA为系统增添了智能性,不但能在源端设备(如机顶盒、DVD播放器或PC图形卡)与宿端设备(如显示监控器)之间进行功能协调,而且还可优化通信参数。

扩展显示识别

DisplayPort一个特别重要的特性是,能够通过VESA的增强显示识别数据(EDID)结构与不同的设备进行接口相连。EDID并不是什么新事物。实际上多年以来设计人员一直在使用各种视频接口读取EDID的宿端设备参数,从而与设备进行接口连接。不过这些早期的EDID及相关接口技术通常不包含高级可配置通信通道。如今借助DisplayPort,VESA为系统增添了智能性,不但能在源端(如机顶盒、DVD播放器或PC图形卡)与宿端设备(如显示监控器)之间进行功能协调,而且还可优化通信参数。DisplayPortv1.1a可协调的变量包括通道数量(1、2或者4)、每信道数据速率(1.62或2.7Gb/s)、电压摆幅(0.2、0.6、0.8、1.2V)、4个级别的通道预加重以及链路时钟向下扩散。由COREGenerator生成,并与LogiCORE一道提供的接收宿端范例设计可提供范例EDID(图3),以便满足EDID源端设备的读取需求,确保用户的最佳视觉体验。

宿端范例设计在FPGA内部的BRAM中实施了EDID数据结构。DisplayPort的源代码可通过AUX通道实现I2C协议。图3和图4显示了连接至源端的DisplayPort宿端的方框图。宿端的Link与StreamPolicyMaker属于宿端内核的组成部分,不过源端的LinkPolicyMaker具有更高的复杂性,将作为源代码随参考设计提供。EDID通过I2C接口与接受宿端进行接口连接。

I2C协议非常适合针对EDID数据结构的连接,并常常用于这种类型的应用。I2C控制器负责定位与管理在EDID中发现的数据,并通过串行接口与I2C接口协议(通过AUX通道)将数据传输至宿端内核。在工作模式下,用户无需知晓EDID是否正被访问。用户可通过检测I2C总线来监控ROM的内容。在调试模式下,用户能够修改I2C控制器,覆盖EDIDROM提供的3位内容。I2C提供控制信号,在与适当的开集输出相连时,可提供I2C主接口。宿端内含名为“DisplayPort配置数据(DPCD)”的数据结构,可以存储配置数据并作为宿端与源端都可读写的通信邮箱使用。源端一般使用跨AUX通道的DPCD内容(图3和图4)。

结语

采用MicroBlaze的赛灵思SourcePolicyMakerController系统参考设计经过精心设计,可充分发挥DisplayPort的所有优势,向市场推出功能丰富的显示产品。

参考文献:

[1]XilinxIPCenter–DisplayPortLogiCORE[R/OL]:http://www.xilinx.com/products/ipcenter/EF-DIDISPLAYPORT.htm

[2]QuantumData882EVideoTestInstruments[R/OL],http://www.quantumdata.com/pdf/882E_DP_DS_RevI.pdf

[3]VESADisplayPortStandard[S].v1.1a,2008-1

[4]PhilipsSemiconductors.I2SBus特点.1996(更多I2S:http://www.nxp.com/acrobat_download/various/I2SBUS.pdf)

[5]UG196andUG198.Virtex-5FPGAGTPTransceiverUserGuides

[6]UG386.Spartan-6FPGAGTPTransceiverUserGuide