药品灌装生产前必须对药用玻璃瓶进行检测,把不合格品剔除,才能进行药品的封装。由于我国药用管制玻璃瓶大多数规格千差万别,如瓶高、瓶底和瓶壁的厚度以及药瓶的垂直度等参数,其指标都有较大差异,使用进口设备效果又不太理想。所以,急需开发一套符合我国国情的药用管制瓶检测装置实现空瓶的自动化检测系统。

该系统要求在线检测速度达到25瓶/s,而且要求对管制瓶的瓶底、瓶口、瓶身、瓶体尺寸等多个项目指标进行检测和实时处理。因此,对数据采集、存储、传输速度和处理速度及精度提出了较高的要求。

常用的数据采集方案往往采用单片机或DSP作为控制器,控制模/数转换器(ADC)、存储器和其他外围电路的工作[1]。但由于单片机本身的指令周期以及处理速度的影响,难以达到多通道高速数据采集系统的要求。虽然DSP可以实现较高速的数据采集,但是频繁的中断影响了DSP的性能,同时,也增加了系统的成本;另外,实时图像处理系统中,底层的信号数据量大,对处理速度的要求高,但运算结构相对比较简单,很适合采用现场可编程门阵列(FPGA)以硬件方式来实现;高层处理算法的特点是处理的数据量相对较少,但算法、计算公式和控制结构要复杂得多,而DSP能够满足要求。

因此,本文采用FPGA+DSP结构的多通道高速数据采集与实时图像处理系统的设计与实现方案。

1 系统硬件结构设计方案

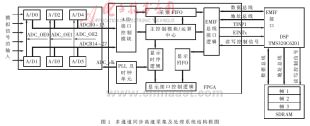

本文设计的多通道同步高速采集及处理系统结构如图1所示。该系统由采集、处理、显示和系统控制四个模块组成。采集的多路模拟视频信号经A/D阵列转换后,输入到处理模块中进行图像处理,处理结果经D/A转换后,显示在终端监视设备上。整个过程(包括采集模块、处理模块、显示模块)都在系统控制模块协调下进行。

2 采集模块

通常的多路数据采集方案[2]是:(1)采用多片ADC器件,每路模拟输入对应1片ADC。(2)采用1片高速ADC器件,由多路开关选择后送给ADC。一般采用CPLD或FPGA控制各ADC或多路开关的方式达到高速采集的目的。但是,采用以上的方案均存在一些问题:相应外围电路庞大,接口复杂;一般都外挂数据缓冲区,降低了系统的传输速度,同时对于高精度、多通道、并行转换A/D系统,使接入FPGA的管脚数增多,这样造成FPGA等系统资源的严重浪费和成本的增加。

本系统采用了一种共享总线、同步采集、分时读取的方法[3],提高了系统采集和传输速度,达到对多通道、高分辨率并行A/D同步采集的有效控制,合理利用了FPGA系统资源,降低了硬件成本。总线共享、同步采集、分时读取的方法主要是借鉴了分时操作系统的思想,按照时间片对A/D转换结果进行轮循读取。从图1可知,在硬件设计上,多路A/D转换器共享采样时钟信号CLK、读写控制信号AD_wr、片选信号ADC_cs;A/D1、A/D3、A/D5共享一路数据总线ADCB14~27,A/D0、A/D2、A/D4共享另一路数据总线ADCB0~13;A/D0、A/D1共享输出使能信号ADC_OE0,A/D2、A/D3共享输出使能信号ADC_OE1,A/D4、A/D5共享输出使能信号ADC_

OE2。多路A/D转换器共享采样时钟信号ADC_clk、片选信号ADC_CS,保证了采样的同步问题;共享数据总线节约了FPGA管脚,合理利用了FPGA资源,通过分别使能ADC_OE信号,在A/D转换完成后数据有效的时间内,分时读取转换结果,达到了并行采集的目的;不同数据总线的二路A/D转换器共享使能信号,保证在同一时间片内并行读取二路A/D转换结果。

ADC的选择如下:

该系统要求在线检测速度达到25瓶/s,也就是每个瓶的检测时间为40ms。另外,对药用管制瓶的检测其精确度是考虑的重要因素。这对ADC的转换精度和转换时间要求较高。

本文A/D转换芯片采用TI公司的ADS8364芯片,它是专为高速同步数据采集系统设计的高速、低功耗、六通道同步采样的16位A/D转换芯片,共有64个引脚,适用于噪声比较大的环境,其最大采样率为250KS/s;每个输入端都有一个ADC保持信号,用来保证几个通道能同时进行采样和转换,可以对单极性或双极性输入电压进行A/D转换;三个保持信号(HOLDA、HOLDB、HOLDC)可以启动指定通道的转换。当三个保持信号同时被选通时,其转换结果将保存在六个寄存器中;当ADS8364芯片采用5MHz的外部时钟来控制转换时,它的取样率是250kHz,采样和转换可以在20个时钟周期内完成;对于每一个读操作,ADS8364芯片均输出十六位数据;地址/模式信号(A0、A1、A2)决定如何从ADS8364芯片中读取数据,可以选择单通道、周期或FIFO模式;在ADS8364芯片的HOLDX保持至少20ns的低电平时,转换开始。这个低电平可使各个通道的采样保持放大器同时处于保持状态从而使每个通道同时开始转换。当转换结果被存人输出寄存器后,引脚EOC的输出将保持半个时钟周期的低电平;ADS8364芯片采用+5V工作电压,并带有80dB共模抑制的全差分输入通道以及六个4Ls连续逼近的模数转换器、六个差分采样放大器。另外,在REFIN和REFOUT引脚内部还带有+2.5V参考电压以及高速并行接口。ADS8364芯片的差分输入可在-VREF~+VREF之间变化。在信号输入端采用差动运放将模拟输入信号以差分方式输入ADS8364芯片,以有效地减少共模噪声,实现较高的有效采集精度。通过同时置/RD和/CS为低电平可使数据读出到并行输出总线。

ADS8364芯片转换过程为:当ADS8364芯片的/HOLDX保持至少20ns的低电平时,转换开始。当转换结果被存入输出寄存器后,引脚/EOC的输出将保持半个时钟周期的低电平,以提示数据分析处理器进行转换结果的接收,处理器通过置/RD和/CS为低电平可使数据通过并行输出总线读出。在转换数据的接收过程中,ADS8364芯片各管脚工作的时序安排很重要。

3 FPGA逻辑控制功能的实现

FPGA是整个采集、处理和显示系统的逻辑控制核心,主要包括A/D阵列采集控制、数据存储与传输控制、图像的预处理、同步时序产生与控制、图像显示控制、EMIF总线接口逻辑。

根据以上控制要求,系统中采用Altera公司的ACEX1K系列EP1K50芯片。EP1K50芯片是一款适合复杂逻辑以及有存储、缓冲功能的FPGA芯片,最高工作频率可达250MHz。该系列芯片具有效率高而又廉价的结构,其特点是将LUT(查找表)和EAB(嵌入式阵列)相结合。基于LUT的逻辑对数据路径管理、寄存器强度、数学计算或数字信号处理的设计提供优化的性能和效率。而EBA可实现RAM、ROM、双口RAM或FIFO(先入先出存储器)功能。

3.1 A/D控制[3]

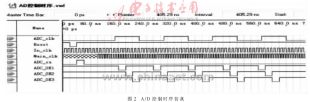

通过上面对A/D控制的分析可以知道,在采样时钟CLK为高电平的半个时钟周期内,读取转换结果是可靠和稳定的。由于片选、地址建立时间以及输出激活时间的要求,在5MHz时钟信号的半个周期内,以共享总线方式可以控制三路A/D转换器。因此,通过两路总线,就可以完成对六路并行数据的采集。图2为三路A/D转换器共享数据总线的控制时序图,采用QuartusⅡ仿真工具完成。其中,ADC_OE1、ADC_OE2、ADC_OE3为三路A/D输出使能信号,通过分时有效的方法,读取各路A/D转换结果,每个时间片长度为30ns;ADC_clk为A/D采样时钟;In_clk为外接时钟,经过PLL输出Main_clk作为系统的主时钟,时钟周期为10ns;ADC_cs为A/D片选信号,该信号建立需要一定时间,为实现多路A/D并行采样,将六路A/D片选信号连接在一起,一直有效;Reset为FPGA复位信号。

来自CCD传感器的图像信号经过ADS8364芯片进行转换,转换结果连同分离出的行同步信号、场同步信号、奇偶场信号进入FPGA。红外光电感应信号也送入FPGA,与同步信号一起作为系统采集与逻辑控制的依据。

3.2 数据存储和传输控制

药用管制瓶检测系统对精度和速度有较高的要求,为了使系统做到高速数据采集和实时数据处理,即采集与处理并行运行,需要在A/D和DSP之间加入缓存设备。一般采用双端口存储器或者双寻址存储器作为缓冲设备[4]。利用双端口RAM虽然硬件设计很方便,但价格较高。而双寻址方法对硬件设计要求较高。因此,本系统采用在FPGA内部设计嵌入式缓冲存储器的方案。考虑到FIFO具有更快的读写速度,同时由于采样写FIFO速度与DSP读FIFO速度不一致,所以选择异步FIFO作为缓存储器。

异步FIFO存储器具有以下特点:有两个端口分别用于读写访问,读写速率可以不同,读写操作可同时进行而且不必同步; 数据的写入与读出遵循先进先出的原则,读写的次序是确定的,读写地址完全由FIFO内的地址指针确定,无需提供外部地址。而DSP的EMIF提供了对FIFO的无缝接口能力,从而使得DMA方式的数据传输支持电路的实现变得较简单。

本系统在FPGA内部设计两个嵌入式缓冲存储器采集FIFO和显示FIFO,充分利用了EMIF的数据传输带宽,分别缓冲存储采集和显示的图像数据流。大部分视觉处理系统的采集卡均采用扩充的大容量FIFO,或者外扩大量SRAM和扩充SDRAM作为采集帧存的方案,但降低了系统的传输速度,同时增加了硬件成本。单个的采集FIFO和显示FIFO的设计方案体现了本系统的优点。通过测试证明,系统单个的采集行FIFO和显示行FIFO较好地实现了连续、实时图像的采集和显示。

本系统中数据的基本流向:多路模拟图像信号输入到A/D阵列,FPGA控制A/D阵列中的ADC将其转换为符合ITU-RBT601标准的16bit数字图像流后,经过FPGA硬件实现平滑、去噪等预处理,进入FPGA内的采集行FIFO进行数据缓冲,然后FIFO的HF等信号作为启动DSP中DMA中断的标志信号,请求DSP取走数据,并生成中断信号请求DSP取走数据,然后数据通过EMIF接口写入帧存储器(SDRAM)中,由DSP对其进行相应处理,处理完的数据仍放到SDRAM中。另一方面,由FPGA中主控制模块产生显示逻辑生成行中断信号,DSP响应中断后,由DMA控制器把数据以32bit的宽度写入显示行FIFO,在显示同步时序的控制下,显示行FIFO输出到显示接口,转换为符合ITU -RBT 标准的8bit数字图像信号,最后送解码器解码和显示。

4 基于DSP的图像处理模块

基于DSP的图像处理模块是实时图像处理系统的核心。模块主要包括DSP器件、SDRAM图像帧存储器、Flash程序存储器等。另外,还要有必要的电源控制、JTAG端口、复位控制、时钟系统等。

系统选用的DSP芯片TMS3206201具有高速处理性能及丰富的片内资源,因此在实时图像处理中得到了广泛的应用。TMS3206201是基于TMS320C6X系列的高速定点数字处理芯片,主频为200MHz,峰值性能可以达到2 400MOPS。TMS3206201芯片的结构决定其适合实时图像处理的特点,主要特点[4]有:(1)CPU核由32位通用寄存器及八个功能单元组成,数据在多处理单元之间的传输依靠32个32位通用寄存器。(2)修正的哈佛总线结构。TMS3206201芯片具有一套256位程序总线,两套32位数据总线和一套32位DMA专用总线。灵活的总线结构缓解了数据传输瓶颈对系统性能的限制。(3)专用的寻址单元。地址的产生不再额外占用CPU的时间。(4)内部集成有64KB的程序存储器和64KB数据存储器。如果将图像放入内存,可以提高CPU读取数据和处理数据的速度。

本系统不仅实现图像采集功能,而且还有图像显示功能,因此,对数据的处理和传输速度都有较高的要求。DSP的DMA传输可以间歇地进行,从而能够让DSP有时间执行数据处理等其他任务,从而提高系统性能。DSP芯片C6201DMA控制器具有四个相互独立的可编程的传输通道,允许进行四个不同内容的DMA操作;一个辅助DMA通道负责与主机通信,每个DMA通道可以在没有CPU参与下完成映射空间的数据传输,数据的传输可以在片内存储器、片内外设或外部器件之间进行。

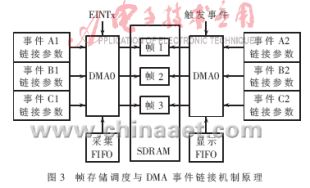

为了保证图像的连续采集和连续显示,在DSP外扩展的SDRAM中设置了三个帧存储区;利用DMA通道在采集行FIFO与SDRAM之间和显示行FIFO与SDRAM之间进行DMA传输。图3为帧存储调度与DMA事件链接机制原理示意图。在采集行FIFO与SDRAM之间,源地址固定不变,目标地址索引加1,利用通道DMA0执行DMA传输,在一帧图像数据存满以后,利用DMA的事件链接机制,使通道DMA0重载事件B1的链接参数寄存器的值,开始接收来自于采集FIFO新的一帧图像数据,且将数据存入SDRAM的帧2中;在存满以后,又重载事件C1的链接参数寄存器的值,接收第三帧图像数据到帧3中,最后再次重载事件A1的链接参数寄存器的值。如此循环,从而实现连续图像数据的采集。同理,在显示FIFO与SDRAM之间,源地址索引加1,目标地址不变,利用通道DMA1执行DMA传输,从SDRAM的帧1、帧2和帧3中,在中断事件的触发下每次读取一行数据,写入FPGA内的显示行FIFO中。利用DMA的事件链接机制,在一帧传输完以后,通道DMA1的链接参数寄存器自动重载事件A2、事件B2、事件C2中的链接参数,实现显示的数据连续传输,从而能够连续显示。

经过实践验证,本系统基本满足药用管制瓶检测系统的精度和速度要求,达到了良好的效果。在应用过程中发现该系统需要进一步研究的工作是:DSP编程需要考虑系统软、硬件资源,应具有实时操作系统的部分功能。因此,算法编程要有很大的技巧,以进一步提高系统性能。

另外,硬件设计方面存在以下几个问题及解决方法:(1)A/D采样电路参考时钟所引入的孔径抖动对系统产生影响,所以考虑选用孔径抖动更小的ECL或PECL门电路来减少孔径抖动的问题。(2)由于FPGA的互连是分布式的,其硬件传输延迟与系统布局有关,会产生一定的毛刺,直接导致产生许多有害的尖峰脉冲。所以,有害尖脉冲的虑除很重要,简单的方法就是加D锁存器。(3)噪声恶化了图像质量,使原本均匀、连续变化的灰度突然变大或变小,形成一些虚假的物体边缘或者轮廓,造成图像模糊、淹没特征,给图像的分析造成困难。可以考虑通过图像预处理来完成,只要图像噪声不是太严重,完全可以通过平滑、去噪的手段达到改善图像质量的目的。

参考文献

[1] 沈兰荪.高速数据采集系统的原理与应用[M].北京:人民邮电出版社,1995.

[2] 张贵清,朱磊.基于FPGA的多路同步实时数据采集方案设计与实现[J].测控技术,2005,24(12).

[3] 张东升,张东来.基于FPGA的高速采集系统设计与实现[J].电子技术应用,2006,32(5).

[4] 李方慧,王飞.TMS320C6000系列DSPs原理与应用[M].北京:电子工业出版社,2003.

[5] Texas Instruments.TMS320C6000 Imaging Developer′s Kit(IDK) User′s Guide[R/OL].2004.