技术进步

由于更高的集成度、更快的处理器运行速度以及更低的价格目标,针对数字电视、线缆调制解调器以及机顶盒的负载点(POL)处理器电源设计变得越来越具挑战性。多年来,随着集成度的提高和工艺技术的进步,设计旨在用于消费类电子应用的数字处理器和模拟ASIC受益匪浅。现在,工艺技术的进步也可用于现成的负载点电源管理电路。本文将讨论一些电源管理设计所面临的挑战,如:选择最佳的输出电容、解决排序问题以及最少化部件数量等问题。为了解决这些问题,通过利用可保持系统低成本的电源管理器件工艺技术的进步,TI开发出了一款新型双通道、降压DC/DC转换器。现在只需要电源设计的基础知识就可以设计出一款高性能电源,从而使设计师将主要精力放在其他重要方而,以使其消费类电子产品更成功、成本更低而且功能更强大。

负载点消费类应用的典型电源架构

非便携式消费类电子设备都是由不同类型的AC/DC电源供电的。例如:线缆调制解调器是由一个简单的墙上适配器供电的,而液晶电视则在其机壳中集成了一个具有功率因数校正(PFC)功能的、可提供数百瓦功率的比较复杂的电源。在上述每个AC/DC电源中,根据具有较大负载电流的系统所需要的最高DC电压,AC电源可转换为常见的DC电压,如:5V、12V或24V。其负载可以是线驱动器、冷阴极灯管(CCFL)背光逆变器或凋谐器模块。

双通道输出电源解决方案

对于消费类应用而言,将两个电源集成到一个芯片上,并采用低引脚数量的小型封装具有诸多好处。大多数消费类应用都需要多个低电压轨来为逻辑电路供电。在这些应用中,双通道转换器可以将单个控制器和两个转换器的MOSFET组合在一个紧凑型器件中。许多ASIC和处理器都需要内核电压和I/O电压,这可能存在排序要求。一款双通道输出DC/DC转换器可以将电路集成,以实现输出电压排序要求的轻松实施。减少DC/DC转换器的数量可以从多方面节约成本,例如:由于在电路板上焊接组件数量的减少,从而加速了产品上市进程,简化了设计、降低了采购限制并提高了可靠性。

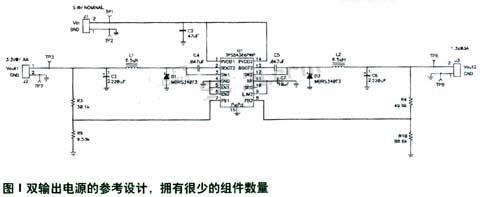

要使双通道、高电流DC/DC转换器成为现实的技术需要考虑诸多设计因素。由于在一个封装中包含了两个转换器,所以要保持器件的低功耗就是一个很人的挑战。如欲实现较小的电路面积,低阻抗MOSFET的集成至关重要,但同时还要满足转换器封装的散热要求。不幸的是,降低电源MOSFET的导通电阻就意味着增大硅裸片的面积,此举会增加芯片的尺寸和成本。DC/DC转换器厂商经常面临着这样进退两难的僵局:要么缩小MOSFET的尺寸以满足芯片小型封装的要求,要么增大MOSFET的尺寸以降低功耗并提高效率。借助一流的工艺技术,TPS54386在尺寸与效率之间实现了平衡——小型14引脚HTSSOP封装中每个MOSFET的导通电阻为85mΩ。对于消费类电子设计师来说,将同类竞争产品宽输入电压范围的DC/DC转换器的导通电阻进行比较,并对其效率进行测量以确保获得最佳值是个不错的想法。图1显示了一款用于双通通道输出DC/DC转换器的典型应用电路,该转换器具有集成的高压侧MOSFET。

虽然使用双通道转换器有诸多好处,但相似的单通道DC/DC转换器通常也有很广的市场前景。当两个低压输出的目标负载之间相隔很火的距离时,使用两个单通道控制器要比使用一个双通道转换器好的多。在高电流的情况下,PWB线迹的电阻会降低负载的输出电压。这样就会影响电源的稳压精度和功耗。在完成电路布局之前,对电路板做一个精心的规划有助于确定是采用一个双通道转换器,还是采用两个单通道转换器更好些。

排序

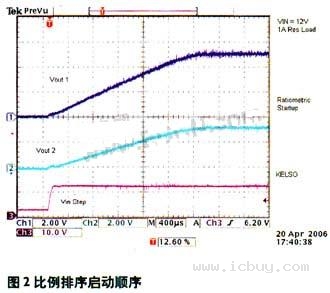

越来越多的处理器厂商开始针对内核与I/O上电时序提供建议的时序指南。除了可以满足内核与I/O上电时序要求以外,对电源进行排序还有助于降低启动时的浪涌电流。当多个电源轨同时启动时,对主电源就提出了更高的要求。如果在大电流充电(charging bulk)时伴随着电流消耗(current draw),且旁路电容非常大,那么主电源可能会跳变至电流限制设置值,从而导致其关断。交错电压轨有助于最少化与浪涌电流有关的问题。为了解决这些问题,图1所示的双通道转换器提供了单独开启的引脚,以适应具体的启动顺序。在向电源输入引脚施加电压以后,可能会使用一个与启动引脚相连的R-C电路来延迟相关输出的开启。此外,排序引脚还允许用户选择顺序排序或比例排序。对于比例排序而言,每个输出端都会在进入稳压的同时,以最终输出电压决定的比例斜坡上升(见图2)。而对于顺序排序而言,当一个输山端实现稳压以后,另一个输出端才开始启动。通过SEQ引脚,用户可以对其中的任何一个输出端进行编程,以使输出端先完成斜坡上升。如果需要的话,开启引脚可以实现单独转换。

缩小外部组件尺寸并减少其数量

近年来,将两个输出电压转换为异相的技术得到广泛青睐。实现两个独立电压稳压器在一个系统中的运行可以共享一个输入电容,并以单个转换器频率2倍的比例吸收(draw)纹波电流。当以180°的相位差运行这两个电压稳压器时,总RMS输入电流被降低了,从而减少了所需输入电容的数量。在此情况下,振荡器频率也实现了内部稳定(该频率是转换频率的2倍)。这两个输出端在内部实现了交互转换周期运行(即以180°的相位差运行)。该技术减少了大体积电容的数量,因此降低了系统成本。此外,通过消除两个转换器之间的拍频(beatfrequency),同步技术还减少了EMI。

DC/DC转换器可以用来实施反馈网络中的内部或外部补偿。外部补偿提供了选择各种电感与电容组合的灵活性,但是对于那些不擅长模拟设计的数字设计师来说,控制环路补偿与稳定性判断标准无疑是非常麻烦的。在此方法中,首先是要选择LC滤波器,然后再决定补偿网络。内部补偿不但简化了设计,而且减少了外部组件的数量,但是设计师必须在一定的LC组件范围内进行选择。因此,必须选择适当的LC滤波器,以保持稳定性。为了降低设计和生产成本,该转换器集成了补偿组件。这样就可以在提供选择电感和输出电容值灵活性的同时,减少组件的总数量。

使用高阻抗铝电容或低阻抗陶瓷输出大电容

由于成本较低,铝电解质电容在消费类电子领域非常受欢迎。铝电解质电容具有相对较高的等效串联电阻(ESR),其阻值随着温度的改变会发生很大的变化,但是可提供大电容。为了降低总ESR(随之而来的是降低输出纹波电压),必须将若干个铝电解质电容并联起来,这样会占用较多的空间。而相对较小的陶瓷电容则可以和铝电容并联,以降低纹波电压。无论采用哪种方法,都必须对功率级进行适当的补偿。有了内部补偿组件的帮助,如果在输出滤波器中采用了一个高ESR电容,那么在环路响应中就会引入一个零点,这样会导致环路的不稳定。通过引入一个极点(该极点的单个小型陶瓷电容与较低的分压电阻并联),该零点可以被轻松地去除。

最新的陶瓷电容技术已将电容值大大提高,并降低了成本。低ESR陶瓷电容将被用于较高的转换频率,并且是铝电解质电容的替代解决方案。在使用具有内部补偿器件的低ESR陶瓷电容时,需要在反馈网络中添加一个零点以减小交叉频率(crossover frcquency)处的增益斜坡,并提供一个相位升压。可以通过将一个小型电容与上面的分压电阻井联来添加一个零点。

结语

元器件集成度的提高使数字设计师可以专注于主要工作,而将更多的设计任务留给电源芯片厂商。通过在一个芯片上集成多个转换器、集成排序方案并使用低成本滤波器,DC/DC转换器厂商实现了多种功能的集成,从而降低了成本和复杂度。