SEED-HPS6678(HPS6678)是北京艾睿合众科技有限公司新推出的新一代高端DSP+FPGA应用方案。DSP采用TI公司首颗最高主频为10GHz的8核浮点DSP芯片TMS320C6678。FPGA采用Altera 公司的40nm Stratix IV 系列FPGA。通过SRIO协议,DSP可与FPGA的进行高速通信。由于集成了DSP和FPGA各自优点,HPS6678可在高速无线通信、多媒体系统、雷达及卫星系统、医疗系统、高清图像处理等多个领域中发挥重要的作用。

SEED-HPS6678(A)背景

现在比较热门的行业,比如高速通信系统、多媒体系统、高级测量系统、医疗系统和高清图像处理,他们都涉及到高速数字信号处理,而且这也是这些系统的核心所在,产品到底能达到什么样的水平关键就在于高速数字信号处理能达到什么水平。

市场上主要用作高速处理的器件有FPGA和DSP。FPGA编程灵活,具有高度并行体系结构、处理时间可控、高数据率等特点。但是,FPGA也有一些缺点,比如算法相对简单,不能实现很复杂的算法,比如高清图像处理领域识别和控制领域的神经网络控制等等。所以,FPGA更适合处理任务固定重复的应用。

DSP算法处理能力强,它的专长是计算,可以用来实现多条件操作和多算法复杂任务。DSP在处理时需要占用一定的时钟周期,这点对于复杂的算法是可以接受的,但是,如果数据量大,任务重复的时候,会造成很严重的资源浪费,数据处理时间长,数据率低。

综上所述,如果把FPGA和DSP结合起来,采用各自的优点,弥补缺点,这样的系统能在很多领域产生更大的作用。

SEED-HPS6678(A)方案

SEED-HPS6678(A)是北京艾睿合众科技有限公司新推出的新一代高端FPGA+DSP应用方案。

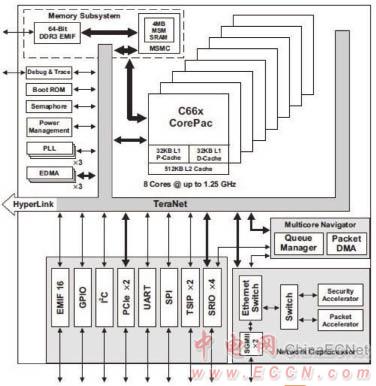

该平台采用TI公司主频最高可达10GHz的多核心定浮点DSP芯片TMS320C6678。此芯片凭借多达8个核心的架构实现超高性能计算能力。每个核都能够达到1.25GHz,8个核相当于达到10GHz。TMS320C6678的功能框图如图2所示。

TMS320C6678的主要特点如下:

• 8个核运行在1.00GHz/1.25GHz 固

定/浮点

•多核结构

•网络处理器,包加速器

•每全双工4×SRIO 2.1Gbaud~5Gbaud

•每全双工2×PCIe 2Gbaud~5Gbaud

•链接50Gband操作,全双工

• 10/100/1000Mbps以太网

• 8GByte 64位DDR3接口(DDR3-

1600)

•16位EMIF-SRAM,NAND和NOR

•两个电信串行端口

• UART接口

• I2C接口

• 16个GPIO引脚

• SPI接口

•十六个64位定时器

• 三个片上PLL

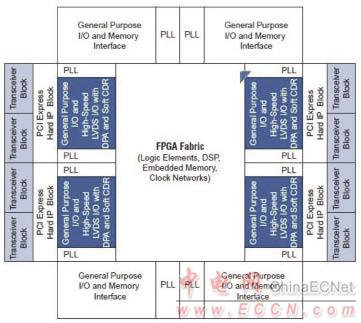

FPGA采用Altera的Stratix IV GX 40-nm FPGA,具有十万级别的LE,11.1Mbits存储器,1288个乘法器以及24个8.5Gbps 收发器和12个6.5Gbps收发器。收发器可以配置成不同的高速接口,Stratix IV GX 40nm FPGA功能框图如图3所示。

图1 SEED-HPS6678(A)方案应用领域

图2 TMS320C6678功能框图

图3 Stratix IV GX 40nm EP4SGX180KF40C FPGA功能框图

图4 SEED-HPS6678(A)功能扩展

EP4SGX180KF40C的主要特点如下:

• 24Gbps~8.5Gbps的全双工收发器

• 12Gbps~6.5Gbps的全双工收发器

•专用电路支持

- PCI Express 1.0/2.0 ×1×4×8

-千兆以太网(GbE)

-串行RapidIO

- SONET/SDH

- XAUI/HiGig

- CEI-6G

- SD/HD/3G-SDI

-光纤通道

- SFI-5

- Interlaken协议

- 175750 Les

• 950 M9K RAM块20 M144KRAM块

• 920 18×18 DSP块

这两款高性能处理器对系统的性能提升并没什么什么帮助,是因为有一个关键的瓶颈,就是数据通信,如果数据通信没有设计好,那么两个高性能处理器没有办法相互工作,就得不到更好的效果,甚至还浪费资源。针对这个问题,采用SRIO协议在两者之间建立一个高速的通路,可以达到速度的3.125×4,这样一来,FPGA和DSP一起工作时候,数据通信瓶颈问题就得到了有效的解决。而且根据SRIO协议的规则,端点处理器可以通过SRIO协议的规则直接操作另一端的存储空间,也就是说,FPGA可以在不占用DSP内核时钟周期的情况下就把数据写入DSP的内存里,等写完后再给DSP发一个中断,表示数据已经写完了,DSP可以处理了。所以,通过SRIO协议,DSP和FPGA可以完成很好的协同工作,我们所要做的是把任务按照FPGA和DSP各自的能力分配给它们,比如算法重复,数据量大的工作可以分配给FPGA去做,而算法复杂多变的任务可以交给DSP去做,充分发挥了各自的潜能,利用了优势弥补了缺点。

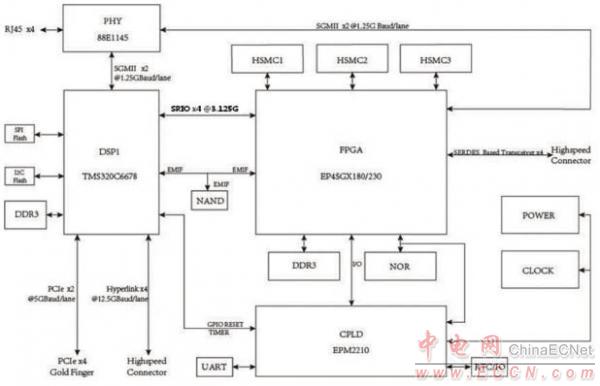

只有SRIO通道,系统还是不完整的,我们根据实际需求在外部扩展了很多重要的部件,如图4所示,给DSP和FPGA各自扩展了1G的DDR3内存,系统在大批量数据处理时能临时存放大批量数据,在DSP需要运行很大的程序的时候也能把程序放在DDR3里。另外,DSP和FPGA都扩展了2个千兆网口,可以让系统直接运用到网络通信场合中,做一些网络协议处理。不仅如此,在DSP端还扩展了PCIE X2的接口,让板卡作为高速PCIE板卡使用,在FPGA还有HSMC X3接口,这个接口是高速差分信号标准端口,具体的信号定义可以由用户自己决定,由于FPGA的编程灵活性,各种不同功能的子卡都能由这些接口获得。

SEED-HPS6678(A)功能架构如图5所示,包括电源部分、时钟源等等。设计时,在芯片选型时要注意时钟的抖动参数是不是能满足DSP和FPGA的要求,尤其是作为高速通信参考时钟的芯片,如果时钟芯片的抖动参数太大有可能会造成高速通信完成不了。在电源选型时需要注意电压和功率,还需要注意电源芯片的杂波等参数。

输入的电源是+12V,3A的直流电源,通过不同的芯片产生不同的电源,在选型时需要注意给DSP外设供电的+1.0V_DSP_AVS(UCD9222)和+1.0V_DSP_FIXED(UCD7242),是专门用于TMS320C6678的。

CPLD采用Altera公司的EPM2210,实现的功能包括上电顺序、复位信号、DSP启动模式、时钟芯片控制和FPGA程序加载。

图5 SEED-HPS6678(A)功能架构

图6 高清视频处理系统

SEED-HPS6678(A)技术亮点包括第一,高端双CPU处理器,即拥有最高10GHz主频的超强TI的8核DSP和拥有36个高速transceivers模块的Altera StratixⅣ GX高端FPGA。第二,DSP与FPGA之间的高速接口,高速串行接口 SRIO(3.125G×4)。第三,灵活的通用扩展接口,HSMC可根据用户需求设计不同高速接口。

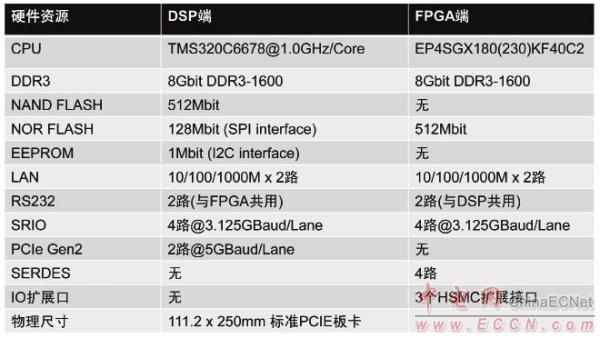

SEED-HPS6678(A)硬件参数如表1所示。

表1 SEED-HPS6678(A)硬件资源

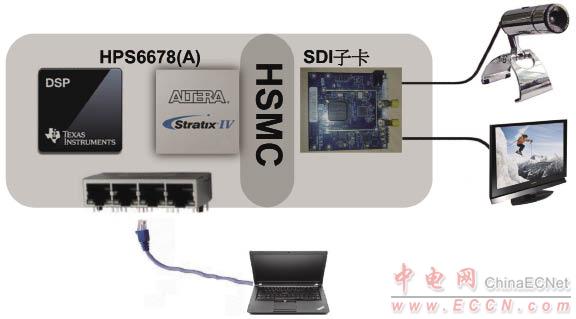

SEED-HPS6678(A)应用

SEED-HPS6678(A)可以用在不同的应用场合,比如高清视频处理系统,如图6所示,这里需要HSMC接口扩展一个SDI视频输入子卡,外部的视频信号可以通过摄像头进入到的FPGA里,在FPGA里,可以对信号进行预处理,比如格式转换、去噪声等,之后,再通过高速SRIO接口让DSP做复杂的处理,比如模式识别,文字提取等等。然后DSP可以通过高速SRIO接口发FPGA回信号,让FPGA把视频信号输出到各种不同的显示设备。当然也可以通过千兆网将视频信号直接发送给PC端。通过这个方案,FPGA和DSP有了各自不同的分工,整个系统效率就会比单个DSP或者单个FPGA要高很多。

在机器人运动控制系统中,如图7所示。SEED-HPS6678(A)也可以发挥很好的作用。机器人除了基本的运动系统以外,还有很多的识别功能,全身有很多的摄像头、位移传感器、陀螺仪等,都可以通过HSMC扩展板卡的方式将这些信号接入到SEED-HPS6678(A)的FPGA里,通过FPGA进行信号整合,然后,通过SRIO接口发送到DSP,DSP通过高速计算,算出机器人最后的姿态再转换为电机的控制量发送给FPGA,由FPGA控制电机。这个系统可以很好地完成机器人的控制。

图7 机器人运动控制系统

在通信领域,如图8所示,通过雷达接收到的信号,通过HSMC扩展一个可以采集信号的AD/DA磁卡,把信号送到FPGA,由FPGA做一个信号的收集和预处理的工作,比如信号滤波和傅里叶变换等等,再把信号送到DPS处理,HSMCADA磁卡是选配的。AD/DA子模块可以配合SEED-HPS6678(A)平台,实现高速数据采集分析系统。其中HSMC接口为高速数据传输的可靠性提供了保证。

图8 通信系统

SEED-HPS6678(A)配套例程及文档包括软件环境:Ti Code Composer Studio (CCSv5.2);Altera(Quartus Ⅱ12.1)。

在DSP方面,配套测试例程有:LED测试例程;UART测试例程

Gbit PHY测试例程;DDR3测试例程;FLASH启动例程;PCIe启动例程。

在FPGA方面,配套测试例程有:LED测试例程;UART测试例程;Gbit PHY测试例程;DDR3测试例程。

配套文档包括原理图和硬件、软件使用指南。

畅学电子

畅学电子