摘要:介绍了一种基于DM648和FPGA构架的图像处理方案,阐述了图像处理模块的组成原理和结构,并对模块内部电路设计和FPGA内部图像处理逻辑进行了重点介绍。木文设计的图像处理模块能够支持对高清视频图像的切割、缩放、叠加和切换等算法处理。

随着数字化时代的到来,视频图像处理作为数字化的重要组成部分越来越重要,特别是对高清视频的处理技术已经成为业界的研究热点。本文针对视频处理技术的特点提出了一种支持多种视频输入输出接口的视频图像处理硬件解决方案。

1 总体结构及硬件设计

1.1 总体结构

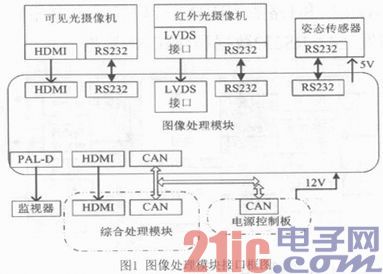

本文设计的图像处理模块主要是用于采集目标的图像信息,并经过图像切割、缩放、叠加和切换等算法处理后,通过HDMI接口把图像数据发送给系统综合处理模块,通过CAN总线接口和RS232接口控制外设和获取外设的状态信息。图像处理模块的主要具体功能如下:接收高清相机的可见光视频信息,视频输入接口为HDMI接口;接收红外摄像机的红外视频信息,视频输入接口为LVDS接口;通过RS232通信接口接收姿态传感器、白光摄像机和红外摄像机等外设的信息;对可见光视频或红外视频信息进行图像处理,并通过HDMI和PAL-D接口进行输出;通过CAN接口接收系统主控板发送的控制命令等。图像处理模块接口应用框图如图1所示。

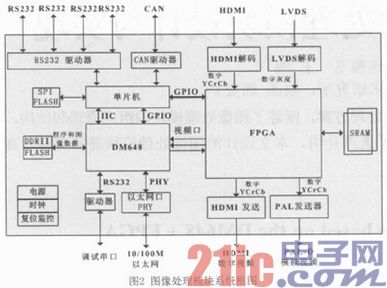

通过分析,图像处理模块的主要功能是进行多路视频处理,并且所处理的视频数据量较大,图像实时性要求较高。因此图像处理模块的实现方案采用DSP(DM648)+FPGA的方式,DSP用于实现复杂的视频处理算法,FPGA的使用保证了图像延时,也有利于系统功能的扩展。图像处理模块的系统框图如图2所示,该模块除过DSP+FPGA的核心电路外还包括HDMI、LVDS解码电路,HDMI、PAL-D编码电路、单片机控制电路、CAN以太网等接口电路。

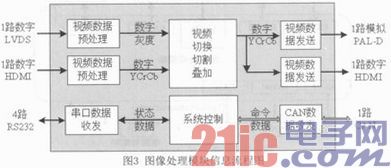

图像处理模块主要完成视频信号的采样、切换和传输功能,同时通过CAN总线接口和RS232接口完成通信功能。图像处理模块的信息流程如图3所示,接收1路可见光相机数字HDMI视频信号和1路红外相机数字灰度视频信号,进行视频数据预处理后,送入到视频切割、切换和叠加等处理单元,处理后的视频数据进入到视频数据发送单元后通过1路模拟PAL-D接口和1路数字HDMI接口发送出去。1路模拟PAL-D接口和1路数字HDMI接口显示内容相同。接收和发送4路R$232数据和1路CAN数据。

1.2 视频解码电路设计

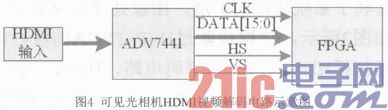

可见光相机HDMI视频解码电路完成1路HDMI输入视频的解码,将解码之后符合高清格式的YCrCb信号送入FPGA,由FPGA实现其它视频处理功能。可见光相机HDMI视频解码电路图如图4所示,采用1片ADV7441来完成视频解码功能。

红外相机LVDS视频解码电路完成1路LVDS输入视频的解码,将解码之后的YCrCb信号送入FPGA,由FPGA实现其它视频处理功能。红外相机LVDS视频解码电路图如图5所示,采用1片National Semiconductor公司的DS90CR286AMTD来完成视频解码功能。

1.3 视频编码电路设计

HDMI视频发送电路完成1路HDMI视频的发送,将FPGA之后的YCrCb信号送入HDMI发送芯片,把并行数字视频编码成串行差分的TMDS物理链路信号。HDMI视频发送电路图如图6所示,采用1片AD公司的ADV7513来完成数字视频的编码与发送功能。

PAL-D视频发送电路完成1路模拟PAL-D视频的发送,将FPGA之后的YCrCb信号送入PAL-D发送芯片,把并行数字视频编码成复合模拟PAL-D视频信号。PAL-D视频发送电路图如图7所示,采用1片国腾公司的GM7121来完成数字视频的编码与发送功能。

1.4 DM648+FPGA核心电路设计

由于该图像处理模块要完成一些复杂的图像处理算法,因此对图像处理器的性能要求较高,本设计的DSP处理器选用了DM648处理器,DM648是TI公司为图像处理应用开发的一款高性能低功耗处理器,它集成了5个可配置的视频输入输出端口和图像协处理器,处理器主频高达1.1GHz FPGA芯片选用的是XILINX公司的SPARTAN-6系列中的XC6SLX100,该系列FPGA具有容量大、高性能、低功耗和低成本等优点,在图形图像处理中有比较广泛的应用。

该图像处理模块的主要是通过FPGA完成视频的格式转换、切割、缩放、叠加等图像预处理功能,通过DM648来完成视频的增强、识别、拼接等复杂算法功能。如图2所示,视频进入模块后,首先进行解码,然后进入FPGA进行预处理,FPGA处理完成后通过视频口进入DM648,在DM648中完成复杂算法的图像处理功能,处理完成后通过视频口再输出给FPGA,在FPGA中完成视频格式转换等功能进行编码输出。下文将对FPGA内部的处理逻辑进行重点介绍。

2 FPGA视频处理逻辑设计

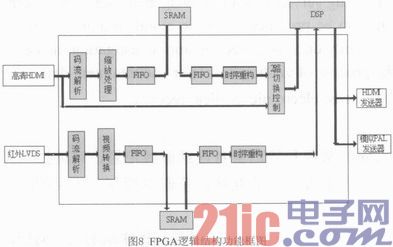

FPGA逻辑结构功能框图如图8所示。可见光相机数字视频解码后的图像信号时序为符合高清规范的16bit颜色深度的YCrCb信号。红外相机数字视频解码后的图像信号时序为基于PAL-D的时序,但在全行像素由768减少到384。可见光和红外的视频数据经过FIFO缓存后存储在SRAM中,然后在FPGA中进行预处理、切割、融合和切换后,送入到DM648的视屏接口,DM648对接收的图像数据进行用户指定的算法处理后,通过视频时序控制逻辑输出到HDMI视频发送器和PAL-D发送器。

可见光相机高清HDMI视频为1920×1080P/25FPS,16位数据信号,时钟频率74.25MHz,数据速率为1.118Gbps,其视频缓存SRAM的总线数据位32位,时钟最高167MHz,本项目设计工作频率为74.25MHz,数据速率为2.376Gbps,是HMDI接口数据速率的2倍,可以满足视频读写缓存的要求。红外相机的视频最终转换成1路PAL视频,用一片SRAM完全可以满足其缓存要求。

3 结束语

基于DM648+FPGA构架的图像处理模块兼有两种信号处理芯片的优越性,有效提高了视频处理的复杂度和速度,增强了视频处理性能,并且具有技术稳定成熟、模块体积小、功耗低等优点。在后续的研究中将深入对基于DM648的图像处理算法进行重点研究,改进算法性能,进一步提高模块的视频处理能力。