摘要:提出一种基于FPGA的空间电场信号数据采集与处理系统的设计方案,FPGA为主控制器控制A/D采样和同步422发送。X,Y,Z三个方向的空间电场信号经过信号处理和A/D采样,在FPGA片内滤波划分为不同的频段,通过同步422接口发送到后续设备。该系统性能可靠稳定,致力于应用在探空火箭有效载荷——箭载电场仪上,对其他电场信号采集与处理系统也有一定的应用价值。

关键词:FPGA;空间电场信号;数据采集;同步422

0 引言

空间电场信号是近地空间很重要的一个参量,它的起伏变化影响到太阳活动、雷暴活动、地震活动及大气环境污染等领域。检测电场的状态可以为航天发射活动提供空间环境的电状态数据,国外发射的许多探测卫星和探空火箭都将电场探测作为重要的科学探测目标。

在传统的探空火箭有效载荷——箭载电场仪中,频道的划分往往采用模拟滤波。模拟滤波电路不仅电路庞大,而且无法克服温度漂移、电压漂移、噪声等缺陷,使得应用领域受到局限。与模拟滤波器相比,数字滤波器精度高,灵活性好,可靠性强,更适合应用在性能较高

的系统。本文提出了应用于探空火箭有效载荷的空间电场信号采集系统,频道划分采用数字滤波处理,应用FPGA内部的有限脉冲响应的IP核,使用FPGA作为主控制器对空间电场信号进行数据采集,发送给后端的公用设备。

1 系统结构设计

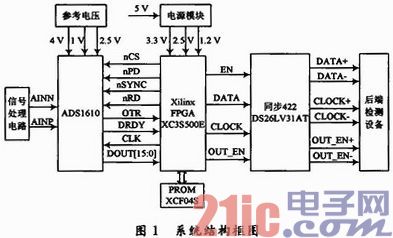

系统结构如图1所示,包括信号处理电路、A/D采样电路、同步422发送电路、电源电路。本文主要介绍传感器后续的电路。FPGA对A/D采样进行控制,整个系统需要5 V,3.3 V,2.5 V等电平,5 V电平由外接电源供给,其他的电平通过5 V转化产生。

1.1 信号处理模块

该模块主要作用是将信号负值电压平移为正值,并将电压电平平移到后端模块可以调整到的幅度范围之内。

该模块包含两级:第一级采用低噪声仪表放大器AD8429,对传感器传输过来的差分信号进行差分放大,AD8429的增益设置计算公式为G=1+6K/RG,其中RG为反馈电阻,对AD8429的增益设置引脚进行开路处理令G=1,相当于将差分信号变为单端信号。其中,由于传感器每个探头采集到的空间电场信号是在-3~3 V范围内,经过差分放大后的信号为-6~6 V,不易于直接输入A/D采样电路中,因此需要经过第二级的处理。

第二级的信号处理包括增加一个+2.5 V的直流偏置和分压处理,运算放大器选用的是国家半导体公司的双通道LM258芯片,电路简单,经过第二级输出的信号幅值在0.5~4.5 V之间,可以直接输入A/D采样电路进行采样。

1.2 A/D采样模块和422发送模块

A/D采样模块是本系统设计的关键,系统性能要求能处理0~1 MHz频带范围内的信号,根据奈奎斯特采样率,本系统选择的ADS1610模块采样率达到10 MSPS,是一款高速、高精度的模拟数字转换器,并且ADS1610的控制信号很丰富,便于FPGA对采样电路进行控制。ADS的电源和地按照推荐电路配置,注意去耦电容放置的位置要离电源和地的输入引脚近一些,电容值越小的离引脚越近,这样使得去耦效果更好,模拟地和数字地之间仅仅在一点用0 Ω的电阻相连。

值得注意的是,ADS需要外围电路提供4 V,1 V,2.5 V三个参考电压,通过运算放大器OPA2822正向输入端输入,经过若干去耦电容后分别进入ADS1610的VREFP,VREFN,VMID三个参考电压输入引脚。

同步发送模块选用DS26LV31AT,如图1所示,由FPGA控制使能信号,输出时钟、数据、输出使能等信号,发送给后端检测设备。

1.3 电源模块

该模块为系统各个模块提供输出稳定的电源。

FPGA供电电压分为3部分,每个bank的电压(VCCO),参考电压(VCCAUX),内核电压(VCCINT)。XC3S500E芯片bank电压为3.3 V,参考电压为2.5 V,内核电压为1.2 V。电源模块选用TI公司的TPS767D325和TPS62003两款芯片,TPS767D325将供电电压5 V转换为3.3 V和2.5 V,提供给FPGA的bank电压和参考电压,而TPS62003则将二级电源3.3 V转换成1.2 V,提供给内核电压。

1.4 FPGA控制器模块

FPGA用来控制A/D采样和同步422发送,FPGA采用的是Xilinx公司Spartan-3E系列的XC3SS00E芯片,它大约有500 k个门,10 476个等效逻辑单元,73 Kb的分布式RAM,360 Kb的块RAM,4个数字时钟管理单元,232个I/O引脚,92个差分I/O引脚。外围电路较为简单,全局时钟从GCLK引脚进入FPGA,保证了系统的可靠性。

XC3S500E芯片的配置芯片选用XCF04,容量为4 Mb,3.3 V的核电压,拥有串行配置接口。

2 FPGA程序设计

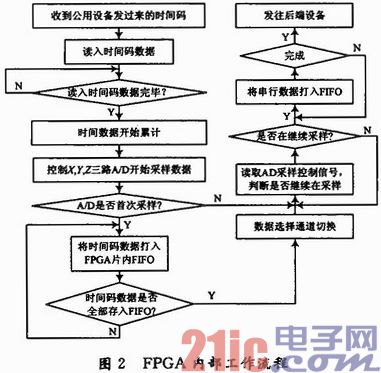

FPGA程序采用Verilog语言编写,主要分为三部分的代码:A/D控制程序、例化FIR的IP核产生数字滤波器、同步422发送程序。FPGA内部的工作流程图如图2所示。

2.1 FPGA对AD1610采样的控制

当不使用ADS1610的时候,可以把nPD引脚置低,这样就关掉了ADS1610的电源,在设计中将nPD引脚置高。ADS1610为并行数据传输,在数据准备就绪之后,需要保持时间来确保上一组数据有效,经过建立时间之后开始接收下一组数据,时序图如图3所示。

引脚nSYNC可以用来同步多片.ADS1610,单片设计时为复位引脚,这里设计不采用多片同步,将nSYNC置低时,ADS1610是异步复位的。当复位的时候,所有的数字电路清零,16位输出引脚DOUT[15:0]被全部置为低,而数据就绪引脚nDRDY被置为高。在程序的设计中,nSYNC在时钟信号的下降沿拉高,则nDRDY在接下来的第二个时钟上升沿拉低。

2.2 数字滤波器的实现

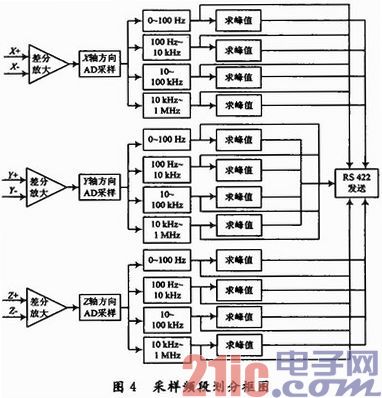

借助Matlab中的滤波器设计和分析工具FDATool,其操作简单、灵活,用户只需在GUI中输入设计需要的滤波器各项参数,就可以获得需要的数字滤波器。本设计中共划分为4个频段:0~100 Hz,100 Hz~10 kHz,10~100 kHz,100 kHz~1 MHz,经实验发现,频带宽度过大的带通滤波器性能不是很理想,通带内幅度并不平坦,失真较大。因此除了第一个频段采用低通滤波器外,另外三个频段采用低通滤波器+高通滤波器的方法来实现,如频带为100 Hz~10 kHz可以用截止频率为10 kHz的低通滤波器和100 Hz的高通滤波器相加得到。将生成的FIR滤波器系数.coe文件导入4个Xilinx ISE中的IP核中,分别例化生成四个FPGA片内的数字滤波器,对X,Y,Z三个方向采集到的电场信号进行频段的划分。

2.3 同步422

将X,Y,Z每个方向的各个通道的滤波后的信号,加上包头、时间码、通道号、校验码之后通过422芯片DS26LV31AT、发送给后端的设备。主要包括两个子模块:波特率产生模块和发送模块。

波特率产生模块:系统外接18.432 MHz晶振,用来产生同步422通信所需要的115 200 b/s的波特率。本模块采用10 MHz时钟。波特率的计算:(1/115 200)/(1/1×107)=86个系统时钟周期,为得到50%占空比的波特率时钟,使得计数器在计数到86/2=43时将输出置高,之后在计数到86时将输出置低并重新计数,就可实现所需波特率的时钟;发送模块:采用状态机进行编写,由五个状态(IDLE,WAIT,STAR T,SHIFT,STOP)和一个进程组成。

3 系统实现

本设计系统硬件设计采用Altium Designer 6.0绘制原理图和PCB图,FPGA程序设计则是在Xilinx ISE 11和Modelsim SE 6.5e平台上设计和仿真,滤波器系数则是在Matlab中的FDA tools工具箱中生成并导入ISE中的有限脉冲响应的知识产权核中。

在系统的输入端加入-3~3 V的模拟输入电压进行测试,进行FPGA片上数据采集处理实验,在每个模块的输出端添加测试焊点,方便逐步调试。系统设计框图如图4所示,根据后端收到的实验数据对比可知,本系统设计完成了设计要求。

4 结语

本文提出的基于FPGA的空间电场信号采集系统应用于探空火箭有效载荷——箭载电场仪探头后端信号采集与处理部分,也可以为地面电场仪处理电场信号提供服务。该方案解决了电场信号采集系统设计要求,避免了模拟滤波电路易受温度、噪声等影响,硬件电路大大简化,可调适性好。经过实践证明本设计方法设计正确,减轻了设计者对于庞大模拟电路的设计负担,系统运行稳定可靠,可移植性强,可用于多种数据采集电路的设计,有一定的参考价值。