摘要:针对超高频(UHF)读卡器在实际应用中容易出现盲区而无法顺利读取标签的情况,提出了应用于UHF读写器的数字跳频技术方案。通过上位机软件发送数字跳频参数给FPGA,FPGA根据得到的参数对集成锁相环芯片Si4133、功率放大器RF2173及外设进行配置,得到数字跳频的栽波信号。测试结果证明,该方案应用于UHF读卡器项目中,能顺利读到标签。

关键词:UHF读写器;RFID;数字跳频;频率合成

引言

RFID技术的发展为物联网的广泛应用提供了技术支持,超高频(UHF)读写器凭借读取距离远、速度快的特点,未来必将在各个行业得到广泛的应用。目前,国内的大部分UHF读写器都是基于单频点或者频带较窄,在读取标签的过程中容易出现盲区,导致无法顺利读取标签。

本文提出了一种基于FPGA的数字跳频技术,通过上位机设置中心频点和跳频步进,利用FPGA对集成锁相环芯片进行配置,得到期望的频率,实现跳频读取标签,从而解决了实际情况中的盲区问题。

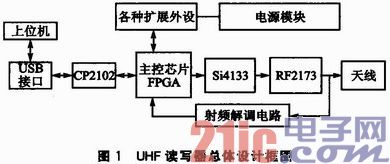

1 总体框架

UHF读写器总体设计框图如图1所示。主控芯片采用Altera公司的Cyclone III系列FPGA芯片EP3C25Q240C8。该芯片有24 624个LE、149个用户I/O口、608 256位存储器、4个锁相环;外部接口多,资源丰富,非常适合在早期研发阶段扩展各种功能。

FPGA外扩512MB SRAM和64 MB NOR Flash存储器,能够实现SOPC设计、操作系统移植、读写器扩展的功能(比如网络接入能力);有USB外设,方便数据的USB传输;利用串口转USB芯片CP2102,可方便上位机软件实现对硬件的配置参数进行控制。

FPGA从上位机发送的命令码中解码出各种配置参数,完成射频发射电路中Si4133中心频率以及跳频步进的设置,对功率放大器芯片RF21 73的工作模式进行选择,实现EPC GEN2协议规定的与标签交互命令的PIE编码和FM0,Miller 2、4、8解码,将读取到的标签EPC通过串口发送给上位机软件,实现人机交互。

2 锁相环芯片Si4133工作原理

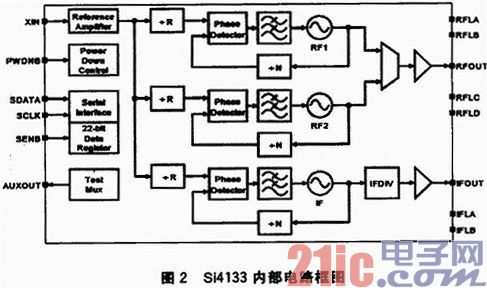

Si4133是Silicon Laboratories公司推出的一款应用于GSM和GPRS无线通信的芯片,内部含有集成压控振荡器的多边带射频频率合成器。其内部框图如图2所示。

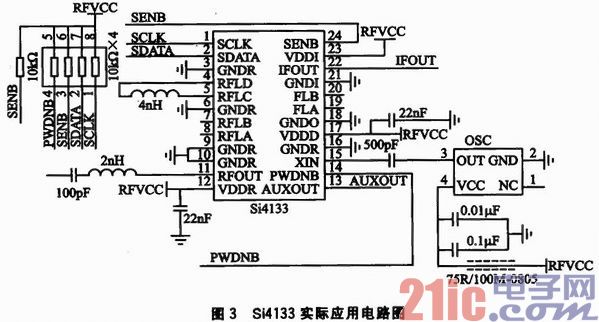

该芯片包含3路独立的PLL,分别由相位检测器(PD)、环路滤波器(LF)、压控振荡器(VCO)以及可编程分频器构成。其中RF1、RF2的输出端口复用,所以RF1和RF2只能由其中一路频率输出。图3为实际应用电路图。

以RF2这一路为例,外部晶振输入频率fXIN经过R分频得到fXIN/R,与输出频率fRFOUT的N分频信号fRFOUT/N一起送入相位检测器进行相位比较,得到一个与相位差成正比的模拟电压u(t),该电压经过环路滤波器得到一个直流分量作为压控振荡器的输入,对压控振荡器进行频率调整。当fXIN/R=fRFOUT/N时,电路的输出频率趋于稳定,实现频率锁定,RFOUT输出频率为 。

。

RF1的压控振荡器中心频率为947 MHz~1.72GHz,RF2的压控振荡器中心频率为789 MHz~1.43GHz,IF的压控振荡器中心频率为526~952 MHz。由于EPC GEN2协议规定的RFID频率为860~960 MHz,故选择RF2生成载波信号,中心频率在920~928 MHz之间进行跳频。

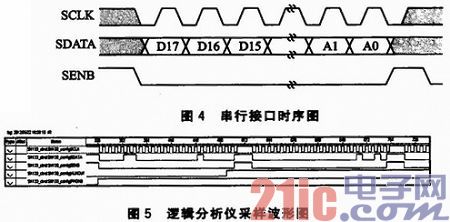

Si4133采用I2C总线对内部9个寄存器进行配置,从而实现软件控制参数。寄存器0~8分别为:主配置寄存器、鉴相器增益寄存器、掉电寄存器、RF1的N分频寄存器、RF2的N分频寄存器、中频的N分频寄存器、RF1的R分频寄存器、RF2的R分频寄存器、中频的R分频寄存器。每个寄存器的写控制字为22位,前18位为数据位,其中高位在前,后4位为寄存器地址,写寄存器需满足图4所示的串行接口时序图。

为利用FPGA内部的嵌入式逻辑分析仪对实际的信息进行采样得到的部分波形图,如图5所示。可以看到,对Si4133进行配置的波形符合时序图,完成了对Si4133的配置,达到了预期的效果。

3 上位机软件设计

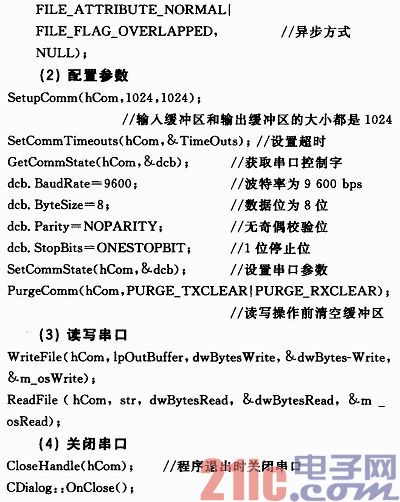

上位机软件采用Microsoft公司的VC++6.0编写,使用API函数方式编程。串口上位机编程分4个步骤:打开串口、配置参数、读写数据、关闭串口。下面详细介绍各个步骤用到的一些函数。

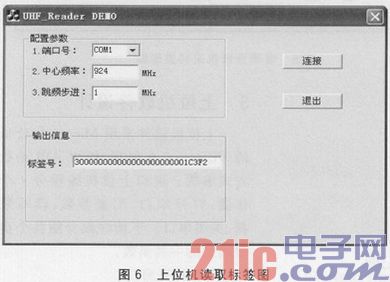

编译通过后,PC机通过串口线连接到FPGA电路板,图6为上位机发送跳频配置参数,FPGA在读取到标签号后,将数据发送给上位机。

4 硬件测试

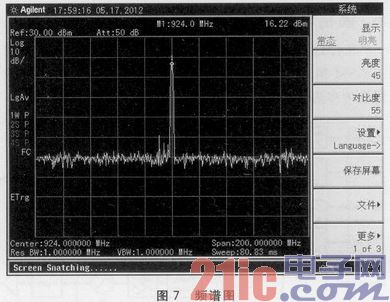

图7为用安捷伦的频谱仪实际测试的频谱图。可以看到,中心频率与软件设置的924 MHz一致,输出功率为16.22 dBm。由测试结果可以看出,功率输出、相位噪声、杂散抑制等都达到较好的效果,应用于UHF读写器项目中,能够顺利工作。通过上位机设置中心频率为924MHz,跳频步进为1 MHz。读取到的标签号为300000000000000000000001C3F2,为十六进制显示,与图6中输出信息中的标签号相同。

结语

本文介绍了如何通过上位机软件发送数字跳频的参数给FPGA,FPGA根据解码得到的参数对集成锁相环芯片Si4133、功率放大器和外设进行配置,得到数字跳频的载波信号。在读取标签的工程中,能够解决之前固定频点时的盲区问题,顺利读取到标签。