基于FPGA的学校打铃器设计.doc

时间:12-27 11:51

查看:1105次

下载:162次

简介:

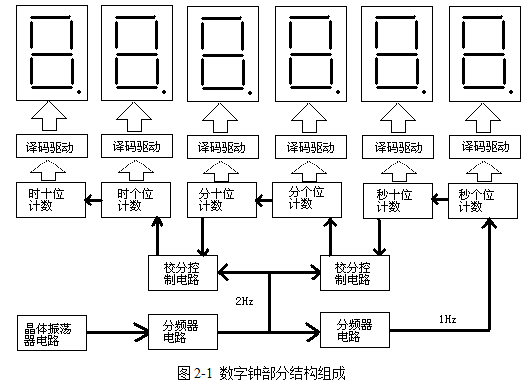

本设计的学校打铃器采用基于现场可编程门阵列(FPGA)的方法,底层模块采用硬件描述语言(HDL)设计,不仅能对时、分、秒正常计时和显示,而且还可进行闹铃时间的设定,上下课时间报警,报警时间1-15秒设置。系统主芯片采用美国Altera公司的EP3C40F484I7器件,由时钟模块、控制模块、闹钟模块、定时模块、数据译码模块、显示以及报时等模块组成,由按键进行时钟的校时、清零、启停等。本文在介绍FPGA器件的基础上,着重阐述了如何使用FPGA器件进行系统的开发,以及如何实现学校打铃系统。通过仿真验证及实际测试,打铃器具有正常计时、定时报警、报警时长设定等功能,可为日常作息提供准确、便捷的提醒。