基于FPGA来完成直接数字频率合成器(DDS)的设计.doc

时间:01-07 11:38

查看:1399次

下载:162次

简介:

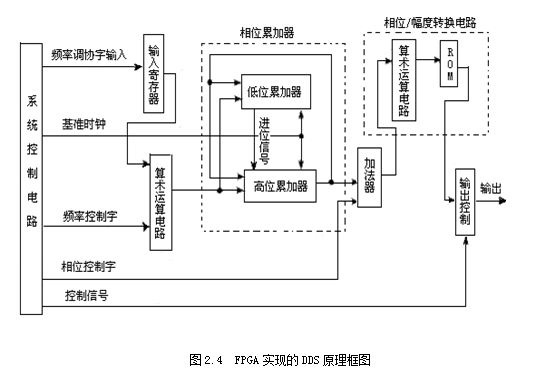

本设计是利用EDA技术设计的电路, 该信号发生器输出信号的频率范围为20Hz~20KHz,幅度的峰-峰值为0.3V~5V两路信号之间可实现0°~359°的相位差。侧重叙述了用FPGA来完成直接数字频率合成器(DDS)的设计,DDS由相位累加器和正弦ROM查找表两个功能块组成,其中ROM查找表由兆功能模块LPM_ROM来实现。而通过设定不同的累加器初值(K1)和初始相位值(K2),可以调节两路相同频率正弦信号之间的相位差,从而产生两路数字式的频率、相位和幅值可调的正弦波信号,最后通过MAX+plusII演示仿真结果。