基于FPGA的高速实时数据采集系统.pdf

时间:04-25 10:27

查看:812次

下载:163次

简介:

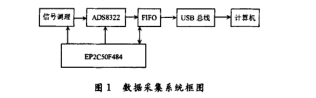

设计一款基于FPGA的高速实时数据采集系统,该系统采用FPGA作为控制器,主要完成通道选择控制及增益设置、A/D转换控制、数据缓冲异步FIFO三部分功能。系统采用VERILOGHDL语言,通过软件编程控制硬件实现通道的选择和可编程增益放大器放大倍数的设置。利用FPGA内部自带的RAM设计16位的FIFO。实现数据的缓冲存储。这种基于FPGA的同步采集、实时读取采集数据的方案,可以提高系统采集和传输速度。系统的仿真验证结果显示,所设计的高速实时数据采集系统达到了预期的功能。