基于FPGA的水声信号采集与存储系统设计.pdf

时间:08-09 10:26

查看:1048次

下载:162次

简介:

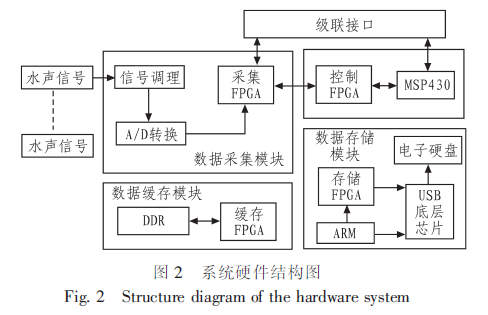

为实现对水声信号的多通道同步采集并存储,提出了一种基于FPGA的多通道信号同步采集、高速大容量实时存储的系统设计方案,并完成系统的软硬件设计。该系统的硬件部分采用模块化设计,通过FPGA丰富的外围接口实现模块间的数据交互,软件部分采用Verilog HDL硬件描述语言进行编程,能够灵活的实现信号的采集及存储。实际应用表明,该设计具有功耗低,可高速实时存储,存储容量大,通用性强,易于扩展升级等特点。