帧存是图形处理器与显示设备之间的数据通道,所有要显示的图形数据首先是存放在帧存之中,然后才送出去显示的,因此帧存的设计是图形显示系统设计的一个关键。传统上,可以用来设计帧存的存储器件有多种,如DRAM、VRAM、SDRAM及SRAM等。DRAM、VRAM及SDRAM属于动态存储器,容量大、价格便宜,但速度比SRAM慢,而且在使用中需要定时刷新。当图形处理器没有外部专用刷新接口时,就需要设计刷新电路,这给系统设计带来不便。SRAM器件高速且接口简单,但是价格较贵、容量小。近年来,随着SRAM容量的不断增大和价格的不断下降,在一些需要高速实时显示的图形显示系统中,用高速SRAM设计图形帧存越来越普遍。本文介绍已在项目中实际应用的采用双SRAM帧存交替切换的高速帧存设计方法。详细介绍应用FPGA设计帧存控制器,实现帧存的交替、上电清屏及借鉴电影遮光板原理实现单帧双扫描的方法。

1 图形显示系统简介

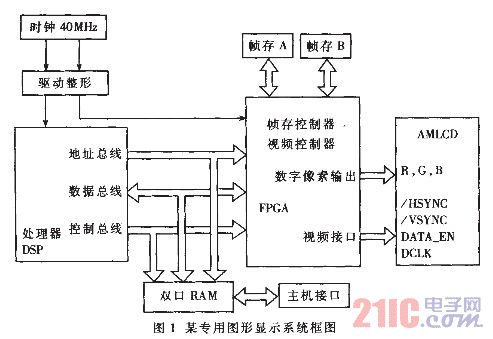

图1是某专用图形显示系统结构框图,图形显示系统采用DSP+FPGA构架。图形处理器采用AD公司的ADSP21061芯片;AMLCD采用Korry公司的KDM710全彩色液晶显示模块,该模块为5×5英寸、600×600分辨率全彩色液晶显示模块,24位数字RGB输入;两个帧存A和B采用IDT公司的71V424L10V高速异步静态RAM(读写速度为10ns)。系统采用双帧存轮流操作方法:当DSP向其中一个帧存写像素时,由FPGA构成的帧存控制器将另一个帧存中的像素顺序读出,送给AMLCD显示;反之亦然。图形显示系统通过IDT公司的71V04双口RAM接收主机的显示信息。图1中的帧存控制器和视频控制器由Xilinx公司的SpartanII芯片XC2S50实现。 视频控制器产生KDM710显示模块所需的一些时序控制信号:行同步信号/HSYNC、场同步信号/VSYNC、数据使能信号DATA_EN和像素时钟信号DCLK等。帧存控制器产生24位RGB颜色数据信号,该RGB数据信号与视频控制器中的时序控制信号相配合,在液晶显示屏上显示出稳定的图形。有关视频控制器的设计方法参见文献[2]。

2 帧存控制器设计

2.1总线切换模块

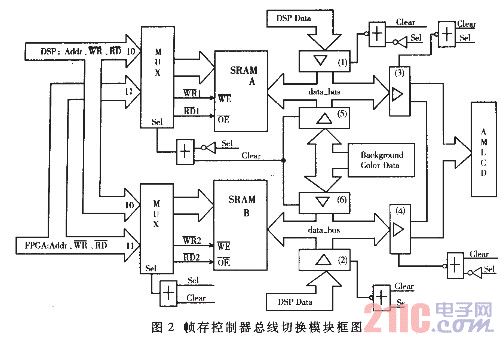

图2为帧存控制器总线切换模块框图。地址总线通过多路选择器(MUX)切换,所有数据总线通过三态门挂在SRAM的数据总线上。帧存SRAM的数据总线上挂着三路数据:一路是DSP的数据总线数据;一路是FPGA的数据总线数据;还有一路是系统上电清屏用的背景寄存器数据系统刚上电时,帧存之中存放的是随机数,画面显示的将是随机画面,需要将背景数据送入两个帧存。总线的切换由体切换信号Sel和上电清屏信号Clear控制。帧存控制器在上电时,通过上电清屏时序将两块帧存中写入背景颜色数据。在上电清屏过程中,Clear信号为高。当Clear为高时,两个地址总线选择器都选择FPGA总线,即FPGA的地址总线指向两个帧存,两个帧存的数据总线全指向背景数据寄存器,即三态门1、2、3和4关闭,而三态门5和6打开。在上电清屏时序完成之后,帧存总线的控制由体选择信号Sel控制。当DSP对帧存A进行写操作时,FPGA所产生的总线对帧存B进行读操作;反之亦然。如图2所示,当Sel为高时,DSP地址总线选择帧存A,三态门1打开,三态门3、5关闭;FPGA地址总线选择帧存B,相应的数据总线三态门4打开,2、6关闭。背景寄存器中的颜色数据可以由用户自己定义。

2.2 控制模块

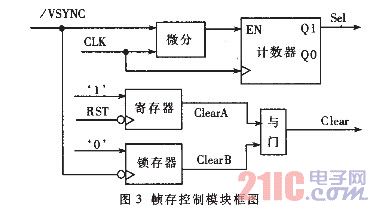

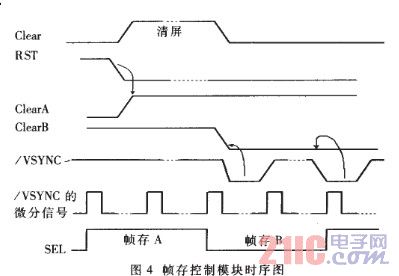

帧存控制器的控制模块产生体选择信号Sel和上电清屏时序信号Clear,控制模块的结构框图如图3所示。图中,/VSYNC是场同步信号,该信号经过一个微分电路,产生一个像素时钟周期宽的使能脉冲信号,控制计数器的计数使能。计数器为一模2计数器,Sel信号为场同步信号/VSYNC的四分频,在出现两个场同步信号之后,才切换帧存,即两个帧存使用的顺序是:AABBAA...这种控制方式类似于电影遮光板的设计思想,使一幅画面在屏幕上重复出现两次,从而在25Hz的帧频时能获得50Hz的场频,使系统视频带宽增加一倍。如当场频50Hz时,图形处理器可以有40ms的时间处理一帧图形数据。图4为帧存控制时序图,Clear信号的产生过程如下:系统上电时,RST信号高一段时间(系统逻辑复位)后变低,在RST的下降沿,ClearA变高,此时场同步低电平有效信号还没到,ClearB为高,Clear为高,系统开始清屏时序。当对两个帧存的清屏工作结束时,场同步信号/VSYNC有效,该信号将"0"电平锁存输出,ClearB为低,Clear为低,系统开始在Sel控制下工作。从控制模块框图中可以看到,Clear信号仅仅在上电复位信号RST结束时(下降沿)才变为高,持续一个场周期之后,Clear信号将一直为低,把控制权交给Sel体切换信号。控制模块的VHDL代码及相应的时序仿真图如图5所示(Modelsim5.5FSE仿真器仿真)。

Entity sel_gen is

Port(clk : in std_logic;

Rst : in std_logic;

Vsync : in std_logic;

Sel :out std_logic;

Clear : out std_logic;

end sel_gen

architecture rtl_sel_gen of sel_gen is

signal clken : std_logic;

signal cleartemp : std_logic;

signal inputrega : std_logic;

signal inputregb : std_logic ;

signal qn : std_logic_vector(1 downto 0);

signal seltemp : std_logic;

begin

process(rst,vsync)

begin

if rst'event and rst='0' then

cleartemp <='1'

end if;

if(vsync='0')then

cleartemp <='0';

end if;

end process;

clear<=cleartemp;

process(clk)

begin

if clk'event and clk='1'then

inputregb <= inputrega;

inputrega <= not vsync;

end if;

end process;

clken <= not inputregb and inputrega;

process (clk,rst)

begin

if (rst-'1') then

qn <= (others = >'0');

elsif clk'event and clk = '1' then

if clken='1' then

if qn = 3 then

qn <= (others =>'0');

else

qn <=qn +1;

end if;

end if;

end if;

seltemp <=qn(1);

end process;

sel <= seltemp;

end rtl sel gen;

3 时序分析

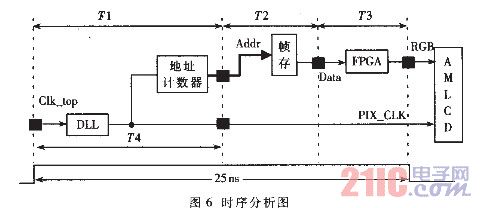

要使高速帧存能正常工作,必须满足一定的时延要求。AMLCD是在像素时钟的下降沿将数据锁存,从像素时钟的上升沿到正确的RGB图形数据出现在AMLCD的数据总线上,之间的延时T必须小于25ns(像素时钟周期为50ns,半周期为25ns),系统才能正常工作,如图6所示。图中的DLL(Delay-Locked Loop)为SpartanII芯片内置的数字锁相环,Clk_top(40MHz)经DLL二分频后得20MHz像素时钟。20MHz时钟一路作为系统工作时钟为FPGA地址计数器提供计数脉冲,一路作为像素时钟直接送至AMLCD。从图6可以看出,延时T包括如下几个延时:T1为Clk_top到帧存SRAM地址总线上地址的改变所需的延时(总线上各个信号的延时是不同的,T1为其中最大值);T2为帧存SRAM从地址改变到有效的数据出现在数据总线上所需的延时;T3为FPGA读帧存数据总线上的数据到输出至AMLCD所需的延时;T4为Clk_top经DLL产生像素时钟直接输出至AMLCD所需的延时。可以看出延时T=T1+T2+T3-T4。系统中的帧存控制器由Xilinx公司的SparatnII 芯片XC2S50-6实现,经过FPGA Express3.7综合和Xilinx公司的ISE4.2I软件布局布线。经分析,布线后的延时:T1=10.994ns、T3=10.691ns、T4=7.784ns,T2 由IS61LV5128芯片的时间参数决定,T2≤10ns,从而T≤23.901ns<25ns,满足系统的时序要求。一般开发工具所得出的时序报告是系统最坏情况下的延时,实际系统中的延时将小于仿真时所得出的数据。

采用高速SRAM存储器作为图形帧存,用FPGA设计帧存控制器,能大大减小电路板的尺寸,增加系统的可靠性和设计灵活性采用双帧存交替切换及单帧双扫技术,提高了系统视频带宽,并能提高系统实时性,减少图形闪烁采用VHDL语言进行FPGA设计具有方法简单、易读和可重用性强的特点。该高速图形帧存已用Xilinx公司的SpartanII系列器件XC2S50实现,并在某型飞机座舱图形显示系统中实际应用。