鳍式场效晶体管的出现对集成电路物理设计及可测性设计流程具有重大影响。鳍式场效晶体管的引进意味着在集成电路设计制程中互补金属氧化物(CMOS)晶体管必须被建模成三维(3D)的器件,这就包含了各种复杂性和不确定性。加州大学伯克利分校器件组的BSIM集团开发出了一个模型,被称作BSIM-CMG (common multi-gate)模型,来代表存在鳍式场效晶体管的电阻和电容。晶圆代工厂竭力提供精准器件及寄生数据,同时也致力于保留先前工艺所采用的使用模型。

寄生提取挑战

然而,每个晶圆代工厂都会修改标准模型以使得更贴切地表现特定的架构和工艺。此外,在这些先进的工艺节点处,晶圆代工厂希望其通过参考场解算器建立的“黄金”模型与该领域设计人员使用提取工具得到的结果有更紧密的关联。在28纳米级节点,晶圆代工厂希望商业提取工具精度介于其黄金模型的5%到10%之间。对于鳍式场效晶体管工艺,晶圆代工厂要求商业提取工具与黄金模型之间的平均精度误差在2%以内,3倍离散标准偏差仅为6%-7%。

最具挑战性的任务是计算鳍式场效晶体管与其周围环境之间更复杂且无法估量的相互之间的寄生数据,这需要涉及前段制程(FEOL)几何结构的精确3D建模。确保三维空间中的精度需要使用3D场解算器进行提取。3D场解算器在先前用于制程特性而非设计,因为其计算成本太高且速率太慢。现在新一代的三维提取工具,比如Mentor的Calibre xACT,通过采用自我调整网格化技术加速计算的方法使其运行速度比之前快了一个数量级。其还有可利用现代多CPU计算环境的高度可扩容架构。有了这些功能,提取工具可以轻松地在32 CPU机器上执行场解算器计算解决方案,小至数个单元大至数百万内嵌晶体管的模块。

在全芯片层次,我们需要考虑数十亿晶体管设计以及几千万根连接导线,即使是快速场解算器也无法提出实用的周转时间。解决方法是采用先进的启发式算法,对于复杂的结构采用场解算器,对于一般的几何图形可采用基于表格的提取方法 (table-based)。这种方法是可行的,由于在布线网格中的电场模型类似于前制程节点所见的。在最理想的情况下,设计工程师所用的提取使用模型不会改变,因为提取工具会自动在场解算器和表格方法之间移动。

随着双重和三重光罩在从20纳米级节点制造开始中扮演着越来越重要的作用,我们正经历着互连角点(interconnect corners)数量的飞跃。在28纳米,5个互连角点是可能的,然而对于16纳米级,我们预计需要11-15个角点。先进的多角点分析计划可以实现更高效的计算,减少每个额外角点所需的额外计算量。此外,我们可以并行处理角点,以使每一个额外角点仅增加10%的整体周转时间。这意味着15个角点只需要2.5倍的单个角点运行时间。

测试挑战

测试和失效分析是特别重要的,因为鳍式场效晶体管的关键尺寸首次比底层节点尺寸小得多。这使得提高的缺陷水平以及增加良率的挑战日益受到关注。单元识别(Cell-Aware)的测试方法特别适合于解决这些问题,因为它可以锁定晶体管级的缺陷。相对来说,传统的扫描测试模式只能识别单元之间互连件的缺陷。单元识别分析过程建立一个基于单元布局内缺陷仿真行为的故障模型。结果能生产出更高质量的图形向量。当采用单元识别方式自动产生测试图形向量(ATPG),硅验证结果表明从350纳米级到鳍式场效晶体管级的技术节点,明显检测出额外更多的缺陷,超出固定模式及过渡模式。

考虑具有三个鳍的多鳍式场效晶体管。最近的研究建议,这样的晶体管应考虑两个缺陷类型:导致晶体管部分或全部击穿的泄漏缺陷以及导致晶体管部分或完全关闭的驱动强度缺陷。

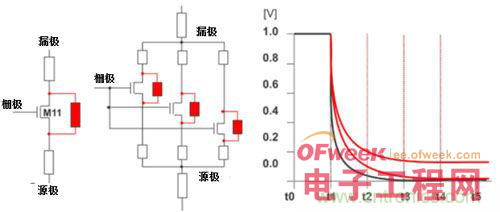

图1:鳍式场效晶体管泄漏缺陷的测试

泄漏缺陷可以通过在每个晶体管的3鳍片两端栅极(从漏极到源极)放置电阻来分析,如图1所示。在单元识别分析过程中,模拟仿真(analog simulation)在一个给定单元库对于所有鳍式场效晶体管的所有不同电阻值的电阻进行。在晶体管在一定门阈值的情况下响应延迟,对缺陷进行建模。驱动强度缺陷可以通过在漏极和每个栅极之间以及在源极和栅极之间放置电阻的方法来分析。至于泄漏测试,模拟仿真通过改变每个电阻的电阻值来进行。每个鳍片的响应时间差异用于决定是否需要进行缺陷建模。其他的鳍式场效晶体管缺陷类型可以通过类似的方法来处理。

鳍式场效晶体管确实带来了一些新的挑战,但电子设计自动化工具供货商和晶圆代工厂会尽全力以对集成电路设计流程影响最小的方式整合解决方案。