一个嵌入式系统的核心在于CPU,当CPU选定后,其他的问题就可慢慢就绪。SoC嵌入式系统的实现可把它分为:一应用型SoC嵌入式系统、开发型SoC嵌入式系统二种型态,这二种型态的软硬体开发有着不小的差异,但首先碰到的都是CPU的选定。这里笔者会针对它们的异同处做说明,再来描述ARM CPU、指令、系统管理、开发实作训练平台(PreSoCes)、Linux与程式等,以建立SoC嵌入式系统的整体轮廓概念,并在实作中培养、训练出开发技能与创新能力。

应用型SoC嵌入式系统是指在一个现成的SoC元件上加入软体(或OS),使成一系统;而开发型SoC嵌入式系统是指SoC元件还在建构中,它会选择仅适用的IP包入并做底层软体测试,以方便未来建立OS,而达成最有竞争力的组合。应用型SoC嵌入式系统所要面对的问题有:选用Turn-key(雏型半成品)方案或自己建构方案、CPU选择、OS选择,以及开发工具、ICE、Debugger、Compiler等的选择,每一种都彼此相关,因此要站在系统产品开发的角度来考量。

假如是选用Turn-key方案,那只要修改部分自己想要的软体即可,这种产品大都属于大量生产又具市场快速反应的特质。软体是系统产品功能的展现,系统大都会挂上一OS,因ARM CPU的设计就是为了放上OS而设计的,因CPU有好几种执行模式以方便task switch用。软体可分为BIOS、Kernel、Device driver、Application S/W等。

在Linux OS上就有Debug的功能,方便软体除错,对于Application软体来说是方便的,但碰上BIOS与Device driver就不足以应付了,就像早期产品开发一样,烧入程式再想想错在哪里,多么没有效率,因此如果有ICE与Debugger工具,那就更有效率了。

至于开发型SoC嵌入式系统大都是SoC IC设计公司的开发型态,SoC的内含是由市场需求而定位出,一个个IP元件再慢慢加上去,并验証之。但问题在于,纯软体的验証实在很难完全达到Co-design的100%验証,在没有更完美的解决之前,其他的方式就因应而生。也由于FPGA技术快速的进步,就把它拿来当成新加入IP功能验証的硬体元件,不仅如此,更方便软硬体整合Co-design的前段功能验証,IP的开发就多了一层保障。

在软体方面,BIOS、Device driver就紧紧地连接着硬体。在这时,当整个OS未建立起来时,就需要ICE与Debugger来帮助CPU驱动程式的除错,以验証程式执行对各IP元件驱动正常否。SoC IP的设计是另一门大学问,就不在此描述。在经过初步功能验証后,SoC IC就慢慢成型,方便日后产出后再加上OS。

在以上二种型态的SoC嵌入式系统中,它的重点不外乎是ARM CPU、OS、ICE和Debugger、FPGA、SoC。当然不一定要用ARM CPU,也可採用MIPS或其他的,只是目前全球CPU IP市场佔有率,还是非他莫属。以下笔者就针对这些重点做描述并在实作训练平台(PreSOCes)上展现各重点技术的开发与训练步骤。首先就针对PreSoCes作一简单描述,以方便各重点技术在实作说明时衔接起来。

PreSoCes

PreSoCes

PreSoCes的实作功能有哪些?它是专门针对SoC嵌入式系统开发、训练而设计的平台,它是一个ICE(Pocket ARM ICE或Carrier ARM ICE)、Domingo Debugger、Creator组合而成。系统上特点:一、在WINDOWS环境就能操作Linux 系统,不需另灌一台Linux PC,也就是一台PC就能开发Embedded Linux。二、具有Linux OS Debugging的Debugger。

Creator它的特点很多,但主要有(1).在Creator上,可更换CPU模组,如用不同的ARM CPU,或具ARM Core的FPGA模组,其他的MIPS CPU也是考虑之一。(2).在Creator上,可更换性的週边IP FPGA模组,如:Create Ph-FPGA-XC2S。(3).电流量测,可对CPU、Memory、LCD、Compact Flash、CMOS Sensor、USB、Ethernet等作量测。其他功能特点如下:

CPU:

˙ARM7TDMI S3C4510(Factory out standard)

CPU模组更换:(另选)

˙Create-ARM922T板(另选)、Altera EPXA1 100K Gates

˙ARM9 TDMI S3C2410 CPU板(另选)

˙其他CPU板(另选)

˙其他大容量FPGA 板(另选)

记忆体(Memory):

˙2MB Bytes Flash ROM

˙16M Bytes SDRAM support byte, half-word, word size

˙Access Compact flash card(compact flash card optional)

˙SDRAM Memory Expansion connector

通讯传输(Communication):

˙RS232C port for Debug Console

˙RS232 port for Application

˙RJ-45 10/100 Base-T Ethernet interface

˙USB 1.1 interface

人机界面(Human-Machine Interface):

˙Codec function with Speaker, Microphone circuit

˙CMOS Camera Module

˙4×4 Keypad

˙LED Lamp X 8;7-Seg LED X 4;8 Pin DIP Switch

˙Graphic LCD Display by 4 Level

系统支援(Board System):

˙1*system reset switch

˙1*JTAG connector

˙Real time clock by I2C interface

˙EEPROM 128×8 Bit

˙Clock changeable for CPU

˙可针对CPU、Memory、LCD、Compact Flash、CMOS sensor、Codec、USB、UART、EtherNet、etc作电流量测

週边IP FPGA模组更换:(另选)

˙Create Ph-FPGA-XC2S板(另选)

˙其他FPGA或CPCD模组(另选)

作业系统(Operating System):

˙Running uClinux

˙Others

ARM CPU

ARM CPU在初步了解PreSoCes功能后,就来看看嵌入式系统的核心ARM CPU,在这里以ARM Core S3C4510元件为说明。为何要学ARM CPU呢?因嵌入式系统是软、硬体的整合,它有BISO、Device driver,能不了解CPU吗?又加上如未来要走入SoC IP设计,那又更不能不了解它,所以笔者仅取重点说明。

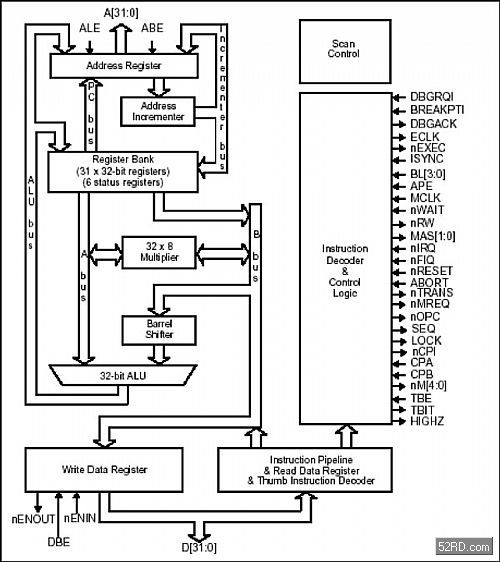

■ARM7TDMI核心的主要组成

〈1〉.暂存器组(register bank):ARM7TDMI利用暂存器组来储存微处理器内部各种操作模式的运算域及CPU状态。暂存器组中的所有暂存器至少具有两个读取埠(read port)与一个写入埠(write port)以供存取暂存器之用,较为特殊是R15,有三个读取埠与两个写入埠。

〈2〉.桶型位移暂存器(barrel shifter):ARM7TDMI利用barrel shifter来执行位元位移或旋转,这是一般DSP常用的功能之一。

〈3〉.算术逻辑运算单位(ALU):ARM7TDMI利用ALU来执行算术与逻辑运算。

〈4〉.位址暂存器(address register)与累增器(incrementer):ARM7TDMI利用位址暂存器与累增器来选择并维持记忆体定址功能,以产生连续或非连续的记忆体位址。

〈5〉.资料暂存器(data register):ARM7TDMI使用资料暂存器来保存资料以与记忆体彼此沟通。

〈6〉.指令解码器(instruction decoder):ARM7TDMI利用指令解码器以产生与指令相对应的控制信号。

图1 ARM core

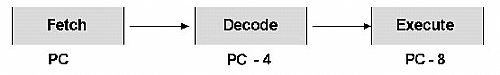

■Pipeline结构

1.完整指令执行的管线作业

2.三层管线作业流程

在这情况下可知一个Cycle执行一个指令。

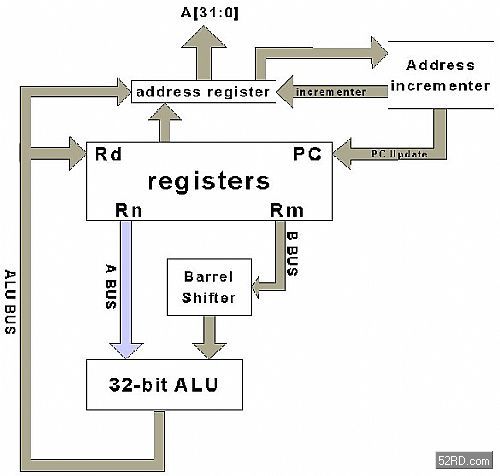

■CPU资料执行图

图2 CPU资料执行

CPU资料执行图说明

本文利用一简单的加法运算再搭配二个暂存器(Rm及Rn)来说明:

1.分别将(Rn及Rm)送到A BUS及B BUS。

2.在B BUS的Rm透过Barrel Shifter作位移运算后,结果与在A BUS的Rn在ALU整合作运算动作。

3.最后运算结果会由ALU BUS送回暂存器Rd做储存。

4.程式计数器结果则透过Address incrementer作更新再将值写回程式计数器。

5.此时Address BUS更新资料位址,进行下一步的命令撷取的动作;记忆体即会把指令送到Data BUS做进一步的指令解码及执行的准备。

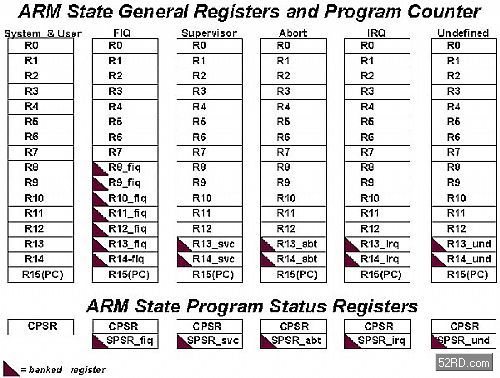

■程式模式(Programmer Mode)

暂存器

ARM Mode暂存器共有37个,分别有31个32bit一般暂存器及6个状态暂存器,而于不同操作模式下分有不同的暂存器可供使用。

表1 ARM Mode暂存器

THUMB Mode暂存器是一个ARM状态暂存器的子集合,分别有21个32bit一般暂存器及6个状态暂存器,使用者可直接使用R0-R7和PC,stack pointer register(SP),link register(LR)、CPSR及SPSR。

在二种State的暂存器组中,有共用暂存器,也有各别暂存器,这就方便OS 的task switch 之程式参数转换用。

■忆体格式

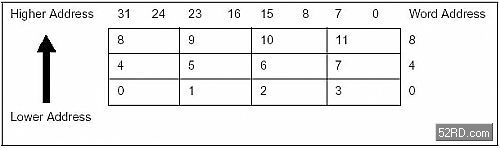

ARM7TDMI对于记忆体内资料的存取以byte为单位,并由0开始线性向上存取的方式进行。也就是byte0~byte3会最先被存取为一个word(在ARM里,一个word等于32位元;也就是4个byte),接下来是byte4~byte7被存取...依此类推下去。而这样储存在记忆体中的一个word之4个byte,哪个会置于最高位置?哪个又会置于最低位置呢?这时,ARM则提供了两种格式供设计者来使用---Big Endian和Little Endian。

在Big Endian格式中,一个word里的最大有效位元组会储存到最低的位元组里,而最小有效位元组会储存到最高的位元组里。

表3 Big Endian格式

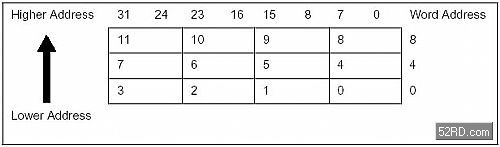

在Little Endian格式中,一个word里的最小有效位元组会储存到最低的位元组,而最大有效位元组会储存到最高的位元组里。

表4 Little Endian格式

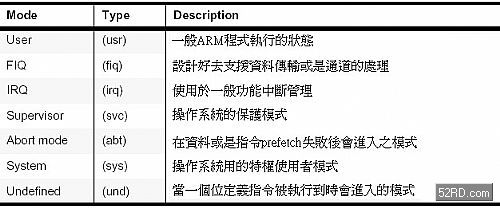

操作模式

ARM7TDMI共支援7种操作模式。

表5 ARM7TDMI操作模式

模式改变

模式的改变可以由软体控制或是经由外部中断和例外事件的处理所产生。大多数的应用程式会在User模式下执行。非User模式,亦可称为特权模式,其通常用来执行中断服务、例外事件,或者是存取受保护的资源。

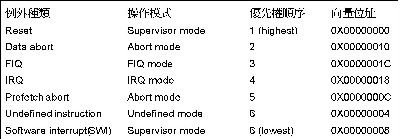

■例外事件

每当例外事件的产生,则程式的一般旗标则会暂时停止,在例外被处理之前,目前的处理程序状态必须被保留,最初的程式才能够被恢復。当中断被处理完时,其他的例外事件就会被接受处理,但它们会依照优先顺序处理。

表6 例外事件

表7 指令中的状态域