0 引言

PCI Express是第三代高性能IO总线,在总线结构上采取了根本性的变革,主要体现在两个方面:一是由并行总线转变为串行总线;二是采用点到点的互连。将原并行总线结构中桥下面挂连设备的一条总线变成一条链路,一条链路可包含一条或多条通路,每条通路由两对差分信号线组成双单工的串行传输通道,没有专用的数据、地址、控制和时钟线,总线上各种事务组成信息包来传送。点到点的互连方式使得每个设备由独立的链路连接,独享带宽,这是提高传输速率的有效解决方案。

随着数量不断增长的PCIe处理单元和外设芯片,PCIE交换和桥接器提供协议转换能力,为这些系统的互连带来了便捷的解决方案,同时丰富了整个应用环境。PLX8648是PLX公司开发的PCIE交换芯片,符合PCIE2.0标准。支持12 port,48 lane,并且端口可以灵活配置、支持多播、低延迟、低功耗。支持热插拔功能,含有三个并行控制器和一个IIC串行扩展模块,配合使用IO端口控制器,可以在每个下游端口实现热插拔控制功能。本文采用PEX8648设计实现了一种可连接多种PCIE设备的数据处理模块。

1 PCIE交换开关

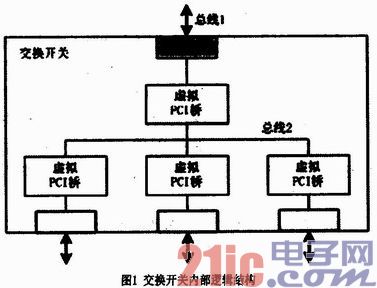

交换开关是一个具有2~n端口的设备,每个端口连一条PCIE链路,在系统中用于多设备的互联。交换开关可以将事务从任一个端口路由到另一个端口,交换开关内部可以抽象为图1的逻辑结构,基于一条虚拟PCI总线,该总线与上游端口及各下游端口间均为一虚拟PCI桥,各桥都采用PCI类型01配置空间头标,配置和枚举软件在系统引导时检测并初始化头标寄存器。

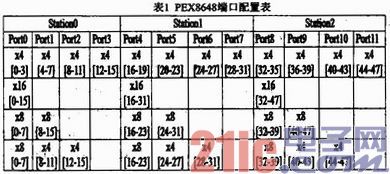

PLX公司的PEX8648最多支持48通路,12端口的PCI Express Gen 2交换芯片,可选择配置每个端口的通路数为X4,X8或X16,也支持X1和x2的通路数,合计480GT/s的带宽。PEX8648交换开关具有灵活的体系结构,48条通路被平均分配在3个控制端口中,称之为Station,每个station包含16条通路,这3个控制端口通过内部互连到中枢RAM中。每个station中的16条通路可以组合,配置成1到4个PCIE端口。如果上游端口在其他station中,则当前station中的端口将使能为下游端口。其端口配置表如表1所示,表中方括号内为通道号。

所有的端口序号都与下游端口内部虚拟PCI总线的PCI-PCI桥分派的PCI设备号相关联,例如端口6是一个下游端口,则内部PCI-PCI桥分给这个端口设备的Device Number就是6。PEX8648的任何一个端口都可配置成上游端口,但推荐将端口0配置成上游端口,PCI-PCI桥对上游端口不设定设备号,该端口的设备号由上游连接的设备分配。

2 模块设计

2.1 功能框图

本文设计的数据处理模块采用PowerPC8640处理器,该处理器配置了两种灵活的高性能IO接口。一种是×1、×2、×4、×8 PCI Expre ss接口,采用PCI-E总线实现板级高性能设备的串行点对点互连。另一种是1×、4×线串行RapidIO接口,本设计中均配置为PCIE接口。处理器对外通过PCIE交换开关互连显示处理芯片和存储控制单元,对外提供4路PCIE链路,可以连接更多的PCIE设备,其功能结构如图2所示。

2.2 PEX8648端口分配

处理器总共连接6种PCIE设备,将处理器第二路PCIE接口上接PEX8648交换芯片,将PEX8648的port0设置成上游端口,配置为×8的PCI Express接口,交换开关下连接PCIE接口的显示处理器,2路对外×4的PCIE接口和2路×1的PCIE接口,5种设备连接的端口号分别现配置如图2所示,Port0为上游端口8640 PCIE1,×8通路;Port4和Port5为×4通路;Port6和port7为×1通路,Port8连接显示处理器,配置×8通路。

2.3 中断号映射

PEX8648支持PCI INTx信号中断机制,它可以向系统中断控制器发送中断信号。这种机制和现存的PCI软件兼容。PEX8648只用INTA#生成内部中断消息,因为他是一个单功能设备,但从下游端点引入的消息可以是INTA#、INTB#、INTC#、INTD#,下游端口内部生成的INTA#中断消息将依照下游端口的设备号在上游端口重新映射。这种重新映射表如表2所示。

根据表2,PEX8648下挂接的5路PCIE接口连接的设备均发送INTA#中断,因此,按照它们连接的端口号分配如下:Port4对应INTA,Port5对应INTB,Port6对应INTC,Port7对应INTD,Port8对应INTA。

处理器PowerPC8640两路PCIE接口在根复合节点模式下接收INTx虚拟中断信号,并将INTx中断信号与中断请求信号IRQn逻辑上进行组合,其映射关系如下

由上表可以得出在系统中断分配时,Port4对应IRQ0,Port5对应IRQ1,Port6对应IRQ2,Port7对应IRQ3,Port8对应IRQ0。

3 PCIE接口软件初始化

PowerPC8640的PCIE控制器上电后需要对配置寄存器以及EP设备进行初始化。首先初始化PowerPC8640的基地址和空间大小。处理器8640在内部定义了多个局部存取窗口,按照优先级选取一个窗口作为PCIE的配置窗口,可设置窗口的基地址和窗口大小。然后扫描PCIE链路上的PCIE设备,这时能扫描到PowerPC8640的PCIE设备,通过看ID号可判定扫描到PowerPC8640的PCIE设备后进行PCIE链路训练,训练通过后进行PowerPC8640的PCIE设备寄存器设置,需要把PowerPC8640的PCIE设备配置为主设备,设置PowerPC8640 的PCIE设备为BUS0,点对点连接的设备为BUS1。

配置完PowerPC8640的PCIE设备后再次扫描PCIE链路,查找链路上的PCIE交换开关PEX8648,PEX8648的总线号是BUS1,找到后再按照类型1配置交换开关头标区,配置原级总线号,次级总线号寄存器和分配给交换开关及所有下游设备的PCI空间基址和大小进行配置,然后对交换开关连有设备的端口的原级总线号,次级总线号寄存器和PCI空间基址和大小进行配置。

配置完PEX8648交换开关后再次扫描PCIE链路,查找链路上的PCIE端节点设备,可以获得BUS4、BUS5、BUS6、BUS7、BUS8上连接有PCIE

设备的ID号,然后各个设备再配置各自的PCI配置空间即可完成PCIE初始化。整个流程图如图3所示。

4 总结

本文通过PCIE交换开关PEX8648实现了多PCIE设备互连的系统,并对PEX8648端口特性、互连方式及软件初始化方法进行了详细介绍。结果表明,基于PCIE交换的处理模块具有灵活的系统拓扑结构,降低了系统硬件复杂度和软件开发过程,可为同行设计提供参考。