本设计采用CSMC 0.5 μm 120 V BCD工艺。不同于传统电流检测电路,该电路直接对电流信号进行处理,输出具有较好的线性度,同时对输入信号基本无影响,并且电路结构较为简单,能够较好地满足IP核应用的需要。通过仿真验证以及流片、测试,证明该电路具有良好的功能性。文中同时给出该电路IP数据提取过程以及后续电路。

1 引言

通常所说的电流检测是用来检测某部件、或者导线通过的电流,一般用互感器、分流器等将电流信号转化成电压信号,然后再对其进行处理放大,作为后面电路保护、检测使用。目前,已经有很多不同的电流检测技术已被公布或实施。其中常用的直流电流检测方法主要是通过串联电阻或者基于霍尔效应原理进行,在通常情况下被测电流信号较大,串联电阻对输入电流信号的影响可以忽略不计,但随着科技发展的需要,被检测信号日渐减小,在系统电路中如果直接串联电阻,会影响前级电路工作,导致被测电流信号的大小发生改变,此时这一影响已经不能再被忽略。

为了检测小电流信号,同时实现将输入的电流信号缩小的功能,以便满足后续处理电路的要求,本文给出了一种不同于传统电流检测电路中常用的两类实现方法--电阻检测和电流互感器检测的检测电路,区别于采用电阻、电容以及电感等无源器件作为主要结构的电路,设计了一款由MOS管为主要结构组成的电流检测电路。它能够在实现电流缩放的同时,克服因对源电流产生较大影响而使得输入电流信号有较大改变的问题。

2 电流检测电路原理及设计优化

2.1 设计要求

本文的设计依托于汽车电子国家项目服务设计平台,项目中要求的电流检测电路主要要求实现将大电流信号缩小,最终得到较小的电流信号输出,以便为后续电路模块提供符合要求的电流值。同时要求,在得到较小输出电流的同时要保证输入电流值不能发生变化。设计要求实现输出电流与输入电流相比达到缩小3600倍的目标,同时要求有较好的线性度。

2.2 结构设计

本文设计的电流检测电路主要是实现将输入电流缩小以便后面对电流进行其他相关操作,比如过流保护等。需要注意的是在得到较小输出电流的同时不能够改变输入电流,或者是对其产生较大的影响,因此不能够直接采用电阻分压的形式。另外还期望该电路电流变化的精度能够达到合理范围,以及具有稳定的输出电流。然而电阻在实际应用中不确定因素较大,温度、工艺等导致方块电阻的稳定性不是很好,波动较大,可能会导致最终流片后得到的电阻值与最初设计有较大偏差,影响电路性能。这两点是该电路设计需要解决的关键问题,也是进行设计的难点。

一般而言,电流镜的一个关键特性是:它可以精确地复制电流而不受工艺和温度的影响,同时这种结构特性本身决定了它对输入电流几乎没有影响。综合考虑上述设计要求以及前端电路输出端的电路结构,最终确定采用电流镜结构实现设计。

在电流镜结构中,Iout与IREF(标准电流,这里即为输入电流)的比值由器件尺寸的比率决定,该值可以控制在合理的精度范围内。需要注意的是,电流镜中的所有晶体管通常都采用相同的栅长,以减小由于源漏区边缘扩散(LD)所产生的误差。而且,短沟器件的阈值电压对沟道长度有一定的依赖性。因此,电流值之比只能通过调节晶体管的宽度来实现。另外,对器件宽度的调节实际上是通过多个单元晶体管并联来实现的,而不是简单地设计改变一个器件的宽度。同时考虑到版图以及工艺对电路性能的影响,在设计时晶体管需要尽量采用对称结构。最终确定的电路结构详见图1.

图1 电流检测电路结构图

根据电路结构可以直接计算得出电路理论上实现电流缩小3600倍。电路中各个晶体管尺寸的最终确定是通过对不同器件尺寸电路的仿真结果对比得到的。

3 优化及其仿真

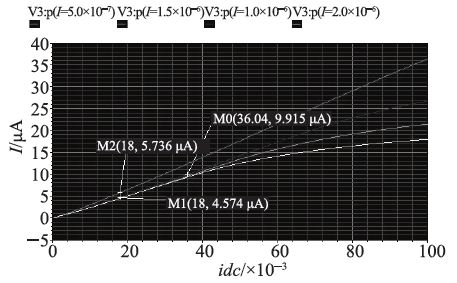

首先确定对于晶体管栅长的选取。根据电流镜结构特点,通常电流镜中的所有晶体管都采用相同的栅长。在设计时还需要考虑最终流片时所采用工艺的要求。本次流片采用的是0.5 μm的工艺,因此L值亦不能过小,否则电路的性能会对工艺准确度有很大的依赖性。通过对不同长度下电路仿真结果(如图2所示)的分析,可以知道在L=1 μm时电路的线性度最佳,能够很好地满足合理的精度要求。

图2 MOS管L值对电路性能影响仿真

综合考虑各方面因素,在选取MOS管的栅长时最终确定L=1 μm为较优方案进行电路的搭建。这也说明了电流镜结构中应采用改变MOS管的宽度调节电流的比例。

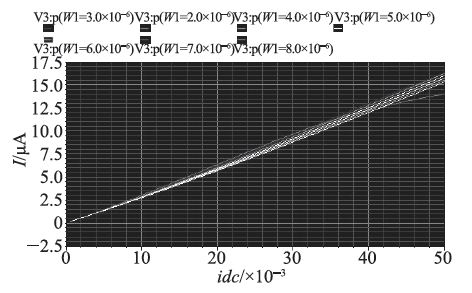

接下来讨论晶体管宽度的确定。晶体管宽度的比例值直接决定了整个电路对电流缩小的倍数。图3是晶体管宽度取2~8 μm依次改变下的仿真结果图。

需要注意的是当宽度较大时,整个晶体管所占面积也会明显增加,另外使用NMOS管和PMOS管的数量也会对电路性能产生一定的影响。所以综合考虑电路变化倍数的需要、精度的要求以及版图面积等多方面因素,最终确定图1中给出的电路结构。

图3 不同宽度下的电路性能仿真

4 性能仿真及测试结果

4.1 仿真结果

首先,对电路的输出特性进行仿真测试。给电路增加不同阻值的负载R1,分别进行仿真测试,观察其输出特性变化,结果如图4所示。

图4 不同R1下的电路性能仿真

从图4中可以很清楚地看到,当电路加载不同负载时电路的输出结果几乎完全重合,说明负载对输出结果基本没有影响。这个结果很好地说明了该电路结构具有很稳定的输出特性,电路设计能够较好地实现稳定输出的设计目标。

同时从图4中标注的两个特殊点可以很好地看出这种电路结构最终实现电路电流变化值与理论值相差较小。对电路进行的后仿真结构与前仿结果相差甚小,所以可以说整个电路在考虑到了工艺波动性的前提下,能够基本满足线性度的要求,正常实现电路功能。

4.2 测试结果

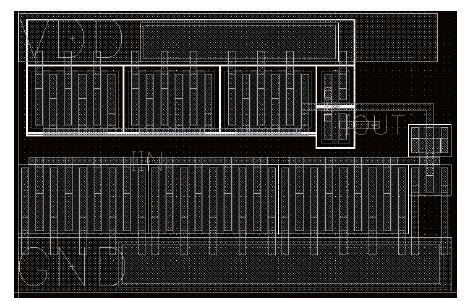

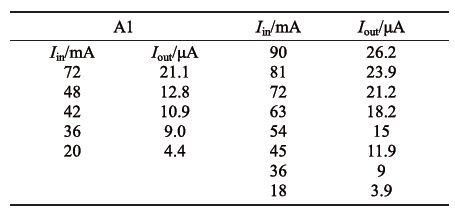

图5为电流检测电路最终进行流片时的版图。可以看到整个电路核心几乎全部是由MOS管构成。表l是对芯片中该电路进行测试的最终结果,由于测试条件限制,只能给出一些不连续的电流值点作为输入。在测试中,我们对多个电路进行了测量,大部分电路的测试结果都比较接近,表l给出了其中较为典型的两组数据。

图5 电流检测电路的版图

表l 较为典型的两组测试数据

通过测试结果可以看出整个电路基本实现了设计的功能要求,完成了将电流缩小的功能。表格中给出的两组数据结果的放大倍数与仿真结果相差不大,基本达到了设计要求。而在实际测试中还出现了一组偏差较大的数据,这些测试数据结果是选取不同5×5芯片内的电路进行测试的。这说明由于工艺问题,不同位置的电路存在着一定的性能偏差,个别电路的性能可能不是十分理想。但这是在设计考虑之内的工艺偏差,同时也说明了该工艺存在着不稳定性。

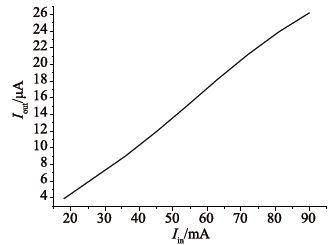

为了更直观地看到电路电流变化特性,我们将表l的第二组数据绘制成曲线,结果见图6.通过数据整理计算,可以知道测试结果与仿真结果相差1 μA左右,并且当输入电流值越大,偏差会略有所减小,相对得到的输出电流的精度越高。整个电路能够较好地实现电路缩小功能,并且能够达到设计要求的3600倍的缩小值。同时测试结果的线性度在合理范围之内。

整体上,最终的测试结果是可以被接受的,这说明电路能够较好地实现其功能。

5 数据提取

随着信息产业的飞速发展,IP核的使用日益受到业界关注。据Dataquest统计,IP核已经成为一项产业。而该电路的设计正是为了实现IP核模块的设计,所以在完成基本的电路设计以及流片、测试工作之后,还要对相关数据进行打包处理,以便于IP核的复用。数据处理包括提取电路的LEF文件以及逻辑功能(Verilog-A代码)的编写工作。

图6 电流检测电路测试结果图

LEF文件的产生使用的是Cadence公司的数据提取工具Abstracts Generating进行IP核数据提取。Abstract主要根据三种基本数据--TECH.lef、需要提取的各电路版图信息(GDSII)和MAP对电路各种器件、管脚信息进行提取,得到lef文件abstract.lef.

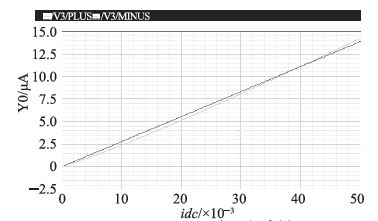

逻辑功能是用一种高层次模拟电路硬件描述语言Verilog-A代码进行编写的。图7展示了该代码经过仿真验证结果与上面电路结构的仿真基本一致,说明所写代码能够正常实现电流检测的功能。这样就完成了对该电路逻辑功能的编写以及数据提取的基本工作,为IP核的复用提供了数据支持。

图7 VerilogA代码仿真结果

6 结语

本文中的电流检测电路采用有源器件完成电路设计,基本实现了电流检测的功能,在电路设计过程中综合考虑性能要求以及工艺限制进行结构的优化。