与通用集成电路相比,ASIC芯片具有体积小、重量轻、功耗低、可靠性高等几个方面的优势,而且在大批量应用时,可降低成本。现场可编程门阵列(FPGA)是在专用ASIC的基础上发展出来的,它克服了专用ASIC不够灵活的缺点。与其他中小规模集成电路相比,其优点主要在于它有很强的灵活性,即其内部的具体逻辑功能可以根据需要配置,对电路的修改和维护很方便。DSP+FPGA结构最大的特点是结构灵活,有较强的通用性,适于模块化设计,从而能够提高算法效率;同时其开发周期较短,系统易于维护和扩展,适合于实时数字信号处理。本文介绍的就是一种可以应用于军事侦察的红外动目标识别跟踪系统的设计。

设计任务及要求红外动目标跟踪与识别系统的输入信号是红外摄像机提供的模拟或数字视频信号。该系统通过基于C6X系列高速DSP的数字视频处理卡,实时的处理红外数字视频序列,完成对运动目标的搜索、捕获、跟踪、记忆;并且在PC上实时显示红外视频图像,实时给出运动目标的空间坐标,产生运动目标区域的特征数据,完成运动目标区域图像的实时存储或远程传输。硬件模块需要为系统功能的实现提供硬件支持,即提供与系统功能相适应的底层物理支持,包括运算处理速度、存储容量等。

模拟视频数字化精度要求:AD精度为8bit;数字视频通道的要求:按RS422传输协议接收数据,像素精度14bit;每场图像处理时间<40ms;搜索到捕获时间:0.2~1s;捕获到跟踪时间<120ms;25帧/s实时识别、跟踪运动目标(即当前场数据必须在下一场数据到来之前处理完毕,并由计算机输出处理结果,显示视频图像),并给出目标位置及领域图像;与计算机的接口为PCI接口。

系统总体设计根据设计任务和系统要求,本系统大致可分为四个模块(见图1)。

图1系统模块组成

UNIT 1模块基于标准32位+5V的PCI总线,并配以超大规模可编程芯片(DSP,FPGA),具有极强的运算、处理能力。

UNIT 2模块的功能主要实现是运动背景下的动目标检测、跟踪。考虑到系统的实时性要求,运动背景下的动目标检测采用基于摄像机运动补偿的差分技术。首先对摄像机运动造成的全局运动进行补偿,对补偿后的序列图像进行差分运算;然后在差分域搜索目标运动引起的运动扰动区域;最后在原视频图像上分割提取运动目标。同时,采用预测技术对目标的可能位置和存在区域进行估计,以实现实时、准确跟踪(或记忆)目标。系统软件按照其工作状态分为四个状态模块:搜索、捕获、跟踪、记忆跟踪。系统按照搜索、捕获、跟踪、记忆跟踪四个状态及其转换运行,以实现运动目标的实时检测与跟踪。

UNIT 3模块的主要功能是实现硬件模块与上层应用程序的数据通信与信息交互。系统采用了PCI 9054 Target方式的单周期读/写;在图像数据传送的时候为了满足每秒25帧图像的实时传送和处理的要求,采用了PCI 9054的Scatter/Gather DMA方式的数据传输。在整个系统的信息交互中,采用了一次握手协议,也就是请求一一应答协议。

UNIT 4模块的主要功能是向硬件模块下载DSP跟踪程序,启动/停止DSP,实时显示场景视频,对运动目标序列进行实时存储,对运动目标序列的基本特性进行实时分析和结果的显示。

系统硬件设计系统硬件原理框图如图2所示,为了设计和描述的方便,我们把硬件模块的电路结构划分为以下几个单元:视频接口单元、输入输出FIFO视频图像存储器、数字图像处理单元(DSP)、可编程控制器、与PC的PCI接口电路等。

图2系统硬件原理框图

1视频接口单元

红外运动目标识别与跟踪系统的视频源是红外摄像机提供的视频信号。红外摄像机有两路视频输出,即模拟视频输出和数字视频输出。本系统要求硬件模块对两路视频信号都能够进行处理。因此,必须对输入视频信号进行预处理,为数字图像处理单元(DSP)提供必要的视频数据和视频同步数据。视频接口单元框图如图3所示。

图3视频接口单元框图

2输入输出缓冲FIFO

设置输入输出缓冲FIFO的目的是在高速器件和低速器件之间设置一个缓冲区,可以避免高速器件因等待低速器件的数据而使系统的效率降低。A/D芯片送出的数字信号的时钟频率约为12MHz(模拟通道时钟12.51MHz,数字通道时钟12MHz),而处理卡上DSP的总线频率高达50MHz,两者差异较大,所以采用输入输出缓冲FIFO是必要的。基于以上考虑,最终选用Cypress公司的CY7C4275.它的容量为32K×18,最大存取速度可达到 l0ns.

3可编程控制器(FPGA)

在本系统中,FPGA控制了绝大部分单元,包括通道选择/电平转换芯片、输入输出FIFO、SRAM、DSP、PCI接口电路等。利用FPGA芯片的系统内可编程(ISP)性能,完成所有DSP外围芯片的控制逻辑;并在其中设置状态寄存器、命令字寄存器和专用寄存器,完成与主机的实时通信,接收主机传送的命令信息和向主机传送所需要的状态信息。

在本系统中,数字信道为14bit,模拟为8bit,需要由FPGA对信号进行第一次装配(区别于DSP为了显示而对图像按FGB格式进行的第二次装配),即将数字/模拟信号/数据均转换为16bit的数据,然后将两个16bit数据装配成一个32bit的数据。

4数字图像存储器(SRAM)

红外动目标识别与跟踪系统要完成对运动目标的识别与跟踪。其实现算法必然涉及到对多帧(差分处理,至少两帧)视频图像的处理。为了给实现算法提供较为充裕的存储空间,我们选用的存储器能容纳6场视频图像。因此,最后选用的存储器是Giga Semiconductor公司的两片GS74116,其每片容量为256K×16bit,存取速度为15ns.考虑到我们视频图像每场的数据量为 76800像素,两片512K的SRAM可以存下至少6张视频图像。在本系统中,我们设置了4帧图像存储空间,其余空间用于存放目标小图、DSP装配数据等,数据空间具体地址分配如图4所示。

图4 SRAM数据空间分配5数字图像处理模块(DSP)

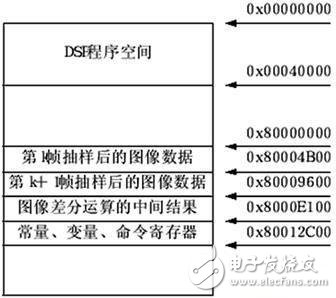

DSP采用TI公司的TMS320C6202芯片。我们采用隔点、隔行的亚抽样。抽样后,每帧图像大小约为20KB,总计约需80KB的数据空间,TMS320C6202的片内数据空间足够所需。我们对DSP芯片的内部空间分配如图5所示。

图5 DSP内部空间分配

function ImgZoom(Id)//重新设置图片大小防止撑破表格{ var w = $(Id)。width; var m = 650; if(w 6 PCI接口电路由于本系统与PC的接口是PCI接口。为了避免受困于PCI接口繁杂的数据传送协议,充分发挥PCI总线的数据传送能力,PCI接口电路采用PCI9054芯片。它是PCI总线专用接口芯片,具有数据传送快、数据传送简单等优点。在33MHz的PCI总线工作频率下,它的最大数据吞吐能力为 132MB/s. PCI9054与DSP的数据交换或通信是通过DSP芯片内部的两个寄存器实现的,即地址寄存器XBISA;数据寄存器XBD.对PCI9054及DSP 芯片而言,它们互相并不能直接访问对方的资源,数据交换必须由这两个寄存器中继,如图6所示。

图6 PCI9054与DSP连接图

系统软件设计首先进行系统上电自检,查看系统各部分是否进入正常工作状态,并将检测结果送往主机。然后对整机系统进行初始化工作,检测命令字寄存器确定图像的输入方式和系统的工作方式,若主机未指定,则进入等待状态,直到操作员指定系统的工作方式为止,系统进入正常工作。系统软件流程图如图7所示。

图7系统软件流程图