一种基于FPGA的IPv6主机数据传输模块设计.pdf

时间:08-25 11:57

查看:1813次

下载:162次

简介:

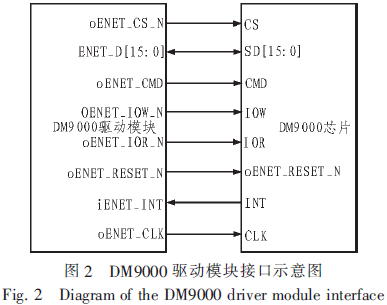

针对在未来IPv6互联网中主机的应用,设计了一种优化缓存结构的精简IPv6硬件协议栈数据传输方案,并完成了硬件方案的Verilog HDL设计和测试的工作。该方案整合了在FPGA上设计的专用集成电路设计(ASIC)以及DM9000芯片,能够在IPv6网络环境中实现无状态地址自动配置、地址解析、回送应答和UDP传输的功能,此外还针对网络主机的结构提出了一种低资源消耗、自我管理的缓存结构。经过测试和应用,该方案UDP传输速率超过28Mbps,并具有可移植性强、资源消耗低、工作稳定的特点,能够满足视频流、音频流等多种大数据量的数据传输。