1 系统应用背景

国家大力推广的智能电网技术是电力行业的技术发展方向,数字化变电站技术是其重要组成部分。完全意义上的数字化变电站的系统将有较好的性能,通过采用电子式互感器,可以消除电流互感器二次开路及饱和、电压互感器二次短路及铁磁谐振、低功耗、安全环保;采用IEC 61850标准,实现不同厂家设备的互操作;二次设备网络化,通信网络取代复杂的控制电缆,降低了铺设电缆带来的电磁兼容等问题。但完全实现以上标准的变电站的投资成本据估算约是常规变电站的3倍。目前110kV以下的中小变电站数量众多,自动化程度较低,对其进行改造是投资的重点之一,但采用全数字化变电站的高成本限制了其推广应用。本文提出了采用低成本实现数字化变电站功能的平台,利用DSP、FPGA等技术做到数字化变电站中的全站传感器同步数据采集,保留了传统的电流电源互感器接口,从而在实现变电站信息化的同时显著降低了其成本,仅为常规变电站的1.5倍。此高速数据同步采集与控制平台除可以用于低成本的数字化变电站系统外,还可应用在其他需要同步监控的系统,如大型风机控制系统、大型锅炉控制系统等。

2 系统硬件组成

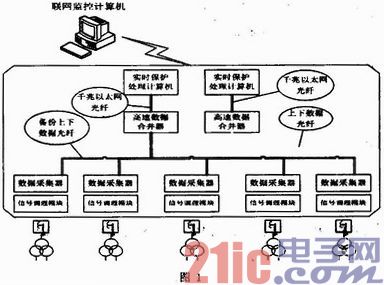

高速数据同步采集与控制平台整个系统的组成主要可以分成三个部分,分别是实时保护计算机、高速数据合并器、传感器数据采集器。根据具体的应用系统,在传感器数据采集器前增加不同的传感器,即可实现不同功能的传感器网络,这里主要对平台三个部分进行说明。系统的工作模式为:在信号调理电路后由数据采集器采集数据,上传至合并器,合并器将数据发送至实时保护处理计算机,由于实时保护计算机采用的是通用的工业计算机,在此不做说明,下面主要对另外两部分进行说明。系统的整体框图如图1所示。

2.1 高速数据合并器

数据合并器的主要工作是产生同步信号,并对64路高速串行上传数据进行同时的接收、合并,并通过以太网实时上传。因此主要有以下性能需求:同步信号的产生;多路高速数图1据接收,64路每路数据流为1638400bit/s;多路高速数据接收下来后以以太网实时上传,速度是25Mbit/s。

项目采用以下解决方案:

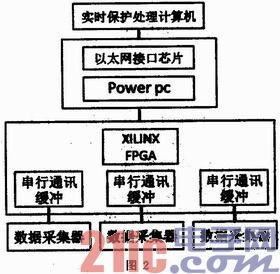

(1)同步信号的产生由单独的MCU处理器来实现,其不仅产生同步信号,同时负责相关数据协议的处理。

(2)高速数据的接收,需要用FPGA的同步处理能力,单独设置64个串行接口模块,分别接收缓冲的高速数据。

(3)高速数据上传也要通过FPGA实现对接收到的数据实时上传至XILINX的XC3S4000来实现。

整个系统的硬件框图如图2所示。

2.2 传感器数据采集器

传感器数据采集器的主要功能是接收合并器的同步时钟信号,并利用AD对传感器信号进行采集,按自定协议将数据通过光纤上传至合并器。主要的指标如下:采样频率为每秒12800次(12.8kHz);每终端需要同时采集8路传感器信号,每信号不低于16位。

采用TMS320F2812的串口来实现同步信号的接收与采集。8路同步采集用8个16位AD来实现。

与合并器的数据通讯同样要考虑光纤模块,考虑保证AD转换16位的精度,所以选择ADS8342。在以上硬件的基础上,系统利用软件完成对传感器的高速数据采集。

3 系统软件部分说明

整个系统的软件组成主要在三个不同设备上实现,一是基于工业计算机板卡的wince上的中心数据处理控制程序,主要实现对采集后的数据的处理运算,并下发控制指令,二是基于XINLINX的FPGA平台的数据汇总程序与指令下发程序,三是基于DSP 2812的数据采集终端部分的数据采集、上传、指令接收等程序。

3.1 数据合并器同步与数据采集程序

数据合并器是对采集器进行下行通讯管理的通道,主要负责产生同步信号的,收集串口数据上传等功能。其中下行信息主要有同步采集时钟信号、时间校准信息、控制信息,以及参数信息。其中以同步采集时钟最为关键,主要是要给采集器一个统一的采集节拍。

对于上行数据而言,采用FIFO原理,将所有的串口缓存进行缓冲,并形成一个按协议要求的数据包,从而实现数据的统一上传。FIFO原理从硬件的角度来看,是一块有两个端口的数据内存,一个端口用来写入数据;另一个用来读出数据。与FIFO操作相关的有两个指针,写指针指向要写的内存部分,读指针指向要读的内存部分。FIFO控制器通过外部的读写信号控制这两个指针移动,并由此产生FIFO空信号或满信号。数据是由某一个时钟域的控制信号写入FIFO,而由另一个时钟域的控制信号将数据读出FIFO。

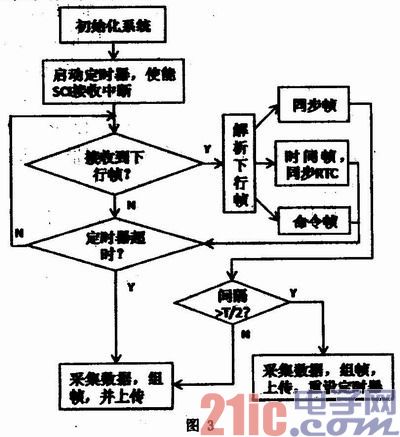

3.2 传感器数据采集程序

传感器数据采集软件的运行主要由两个事件控制,一个是本地定时器;一个是从合并器接收到的下行帧。本地定时器以24×50HZ频率采样,并上传遥测帧;当收到下行帧时,首先解析帧,如果为同步帧,接着判断距上次定时采集的时间间隔是否超过采样周期的50%,如果超过,先采集并发送当前遥测帧,然后重设本地定时器,以同步信号到达时刻为定时起点;如果为时间和命令帧,做出相应动作。流程图如图3所示。

4 结论

本文通过采用FPGA与DSP实现了64路最高通信速率达40MBYTE字节的传感器采集平台,时间同步不大于50μs。传感器采集平台运行良好,有很好的应用价值。