FPGA实现IRIG-B(DC)码编码和解码的设计.pdf

时间:01-19 10:15

查看:960次

下载:162次

简介:

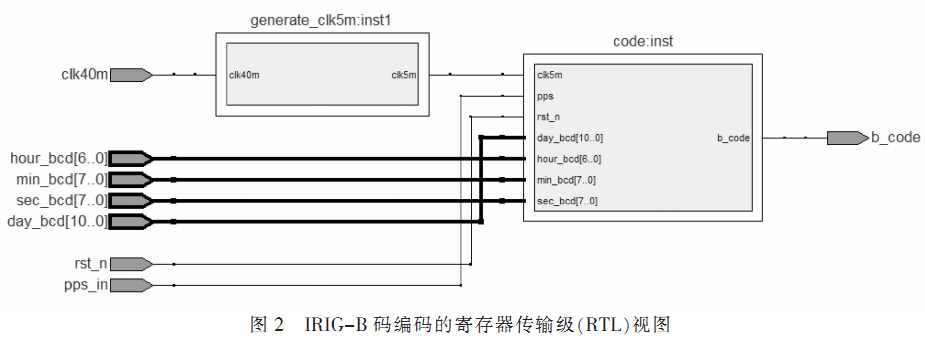

为达到IRIG-B码与时间信号输入、输出的精确同步,采用现代化靶场的IRIG-B码编码和解码的原理,从工程的角度出发,提出了使用现场可编程门阵列(FPGA)来实现IRIG-B码编码和解码的设计方案和体系结构,设计中会涉及到几个不同的时钟频率,FPGA对时钟的同步性具有灵活性、效率高、且功耗低,抗干扰性好的特点。结果表明,FPGA能够确保为从设备提供同源的时钟基准,使时钟与信号的延迟控制在200 ns以内,从而得到了IRIG-B码与时间精确同步的效果。