现场可编程门阵列FPGA(Field Programmable GateArray)属于ASIC产品,通过软件编程对目标器件的结构和工作方式进行重构,能随时对设计进行调整,具有集成度高、结构灵活、开发周期短、快速可靠性高等特点,数字设计在其中快速发展。

本文介绍了一种利用FPGA实现DC~100 MHz的自动切换量程数字等精度频率计的实现方法,并给出实现代码。整个系统在研制的CPLD/FPGA实验开发系统上调试通过。

1 等精度测频原理

频率的测量方法主要分为2种方法:

(1)直接测量法,即在一定的闸门时间内测量被测信号的脉冲个数。

(2)间接测量法,例如周期测频法、V-F转换法等。 间接测频法仅适用测量低频信号。

基于传统测频原理的频率计的测量精度将随被测信号频率的下降而降低,在实用中有较大的局限性,而等精度频率计不但具有较高的测量精度,而且在整个频率区域能保持恒定的测试精度。

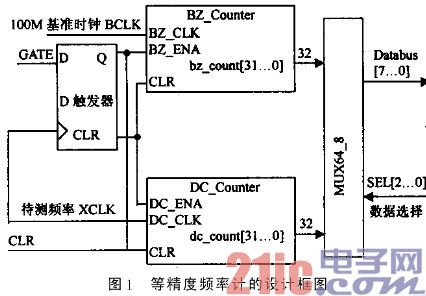

本设计频率测量方法的主要测量控制框图如图1所示。图1中预置门控信号GATE是由单片机发出,GATE的时间宽度对测频精度影响较少,可以在较大的范围内选择,只要FPGA中32 b计数器在计100 M信号不溢出都行,根据理论计算GATE的时间宽度Tc可以大于42.94 s,但是由于单片机的数据处理能力限制,实际的时间宽度较少,一般可在10~0.1 s间选择,即在高频段时,闸门时间较短;低频时闸门时间较长。这样闸门时间宽度Tc依据被测频率的大小自动调整测频,从而实现量程的自动转换,扩大了测频的量程范围;实现了全范围等精度测量,减少了低频测量的误差。

图1中BZ_Counter和DC_Counter是2个可控的32 b高速计数器(100 MHz),BZ_ENA和DC_ENA分别是他们的计数允许信号端,高电平有效。基准频率信号从BZ_Counter的时钟输入端BZ_CLK输入,设其频率为Fb;待测信号经前端放大、限幅和整形后,从与BZ_Counter相似的32 b计数器DC_Counter的时钟输入端DC_CLK输入,测量频率为Fx。

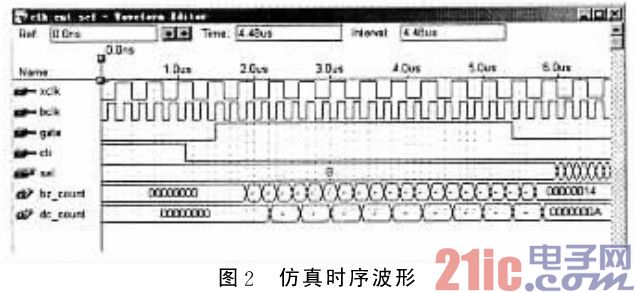

测量开始,首选单片机发出一个清零信号CLR,使2个32 b的计数器和D触发器置0,然后单片机再发出允许测频命令,即使预置门控信号GATE为高电平,这时D触发器要一直等到被测信号的上升沿通过时,Q端才被置1,即使BZ_ENA和DC_ENA同时为1,将启动计算器BZ_Counter和DC_Counter,系统进入计算允许周期。这时,计数器BZ_Counter和DC_Counter分别对被测信号和标准频率信号同时计数。当Tc秒过后,预置门控信号被单片机置为低电平,但此时2个32 b的计数器仍然没有停止计数,一直等到随后而至的被测信号的上升沿到来时,才通过D触发器将这2个计算器同时关闭。由图2所示的测频时序图可见,GATE的宽度和发生的时间都不会影响计数使能信号允许计数的周期总是恰好等于待测信号XCLK的完整周期,这正是确保XCLK在任何频率条件下都能保持恒定测量精度的关键。因为,此时GATE的宽度Tc改变以及随机的出现时间造成的误差最多只有基准时钟BCLK信号的一个时钟周期,由于BCLK的信号是由高稳定度的100 MHz晶体振荡器发出的,所以任何时刻的绝对测量误差只有1/108 s,这也是系统产生主要的误差。

设在某一次预置门控时间Tc中对被测信号计数值为Nx,对标准频率信号的计数值为Nb,则根据闸门时间相等,可得出公式(1):

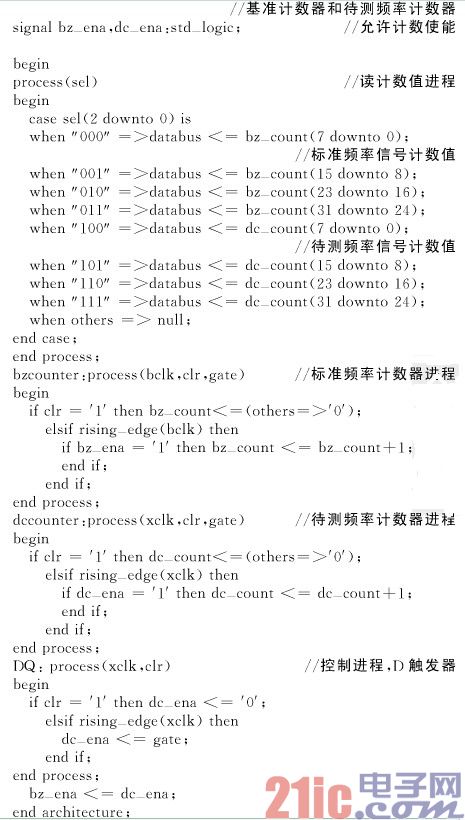

2 频率计的VHDL设计

本设计采用ALTERA公司的FPGA芯片EPF10K10,该芯片管脚间的延迟为5 ns,即频率为200 MHz,应用标准化的硬件描述语言VHDL有非常丰富的数据类型,他的结构模型是层次化的,利用这些丰富的数据类型和层次化的结构模型,对复杂的数字系统进行逻辑设计并用计算机仿真,逐步完善后进行自动综合生成符合要求的、在电路结构上可实现的数字逻辑,再下载到可编程逻辑器件中,即可完成设计任务。下面给出该频率计基于EPF10K10的VHDL描述源程序:

仿真波形如图2所示。

3 结 语

本文利用ALTERA公司的FPGA芯片EPF10K10,使用VHDL编程语言设计等精度频率计,给出核心程序,经过ISPEXPER仿真后,验证设计是成功的,达到预期结果。

和传统的频率计相比,FPGA的频率计简化了电路板的设计,提高了系统设计的实现性和可靠性,测频范围达到100 MHz,实现了数字系统硬件的软件化,这是数字逻辑设计的新趋势。

参考文献

[1]李景华,杜玉远.可编程逻辑器件与EDA技术[M].沈阳:东北大学出版社,2002.

[2]赵雅兴.FPGA原理、设计与应用[M].天津:天津大学出版社,1999.

[3]夏宇闻.复杂数字电路与系统的VERILOGHDL设计技术[M].北京:北京航空航天大学出版社,1998.