摘要:为了满足语音电台抗干扰客观评估系统对语音文件对准精度的要求,在FPGA平台上设计一种基于SOPC技术的带有时间标记信息的嵌入式语音信号录取系统。在GPS接收机时间信息和秒脉冲触发下,NiosⅡ软核处理器控制音频Codec芯片WM8731对输入的音频信号进行高精度采集,将触发时间信息和采集得到的数据按照特定的格式进行打包与封装,并以FAT文件格式存储到SD卡上。由于GPS系统时间信息具有很高的时间精度,加之FPGA器件具有的时序可控特性,使得采集系统所记录的数据具有较高的绝对时间精度,完全能够满足误差小于1 ms的对准精度要求。

关键词:录取;时标;嵌入式;SOPC;NiosⅡ

0 引言

语音通信电台是当今军事指挥、工业调度和日常生产活动中主要的沟通设备,其通信质量与抗干扰能力将对国防和经济建设产生直接影响。语音电台抗干扰客观评估系统(以下简称评估系统)通过数字信号处理算法比较在发送电台端录取的标准语音文件与在接收电台端录取的失真语音文件之间的信号特征,给出语音电台的抗干扰性能参数。由于语音信号是按照每20 ms一个语片进行处理,故对语音信号的对准提出了较高的要求,为了达到较高的评估精度,对准误差应小于1 ms。

为了满足上述技术指标,本文采用当前刚刚兴起的SOPC(System On a Programmable Chip)技术在FPGA(Field Programmable Gate Arr ay)平台上设计了一种带有时标的嵌入式语音信号录取系统。本系统通过捕获GPS(Global Positioning System)系统的授时信息和秒脉冲信号,触发SOPC系统中NiosⅡ嵌入式软核处理器进入外部中断,调用中断处理函数启动音频Codec芯片WM8731,对Line-in通道输入的模拟语音信号进行48 KSPS采样率、16 b采样精度的录取,将触发录取的时间信号作为时标与录取得到的数据按照特定数据格式进行打包和封装,并利用FAT文件系统将封装好的数据存储到SD卡(Secure Digital Card)中。由于GPS秒脉冲前沿可以达到微秒级精度,加之WM8731控制接口采用Verilog语言编写,从而保证了绝对时间误差远远小于1 ms的技术要求。

1 系统组成

SOPC是基于可编程逻辑器件的可重构片上系统(SOC),它集成了硬核或软核CPU、DSP、锁相环、存储器、I/O接口及可编程逻辑,由于具有设计灵活、研制周期短、开发成本低等优点,已经逐步应用在通信、工控、信号处理等诸多领域。

为了给评估系统提供高精度、带有时标的语音数据源,本文采用SOPC技术在FPGA平台设计了一套带有时标的嵌入式语音信号录取系统(以下简称录取系统)。录取系统由片上系统和外围系统两部分组成。片上系统包括:NiosⅡ嵌入式软核处理器、GPS控制器、SD卡控制器、SDRAM控制器、Audio控制器、Ethernet控制器、GPIO控制器以及内部Avalon总线;外围系统包括:GPS接收机M12MT、SD存储卡、SDRAM存储芯片、Audio Codec芯片WM8731、Ethernet物理层芯片DM9000A和传输变压器以及按键和LED等输入与显示器件等。系统组成框图如图1所示。

2 硬件结构设计

在FPGA平台上设计SOPC系统为本文的核心工作。FPGA芯片选择Altera公司CycloneⅡ系列的EP2C35F672C6N,其具有33 216个逻辑宏单元、105个M4K存储单元、4个锁相环以及475个通用I/O口。FPGA开发环境采用QuartusⅡ,嵌入式系统开发环境采用SOPC Buildero由于Nios Ⅱ嵌人式软核CPU、SDRAM控制器、Ethernet控制器和GPIO控制器都是SOPC Builder中集成的通用IP核,直接调用即可,故本文不做详细介绍,下面对GPS控制器、Audio控制器和SD卡控制器进行详细介绍。

2.1 GPS授时系统的设计

本设计中所使用M12MT是一款5 V供电、RS 232电平NAEA 0183格式串行输出、TTL电平秒脉冲(PPS)输出型GPS模块,由于FPGA芯片I/O口是3.3 V电平,故需要进行电平转换,串口电平转换采用美信(Maxim)公司生产的MAX3232芯片,秒脉冲信号由TI公司生产SN74AHC1G04单缓反向器芯片生成。

由于SOPC Builder中的UART核通信协议可以与GPS串口输出协议兼容,故本设计中经过电平转换的信号与片内UART核相连,其参数设为:波特率为9 600b/s、1个起始位,1个停止位,无校验位。秒脉冲经电平转换后与PIO控制器相连,其参数设为输入模式、带有中断功能、边沿触发中断、下降沿触发中断。

2.2 音频采集系统的设计

为了达到较高的录音品质,本设计中选用Wolfson公司生产的音频Codec芯片WM8731,其最高可支持96 KSPS采样率、24 b采样精度的立体声输入/输出。考虑到语音电台抗干扰评估系统的特殊要求和存储空间、处理速度等条件的限制,本设计中通过软件设置,使WM8731工作在48 KSPS采样率、16 b采样精度、单声道的工作模式下。

WM8731的控制接口和音频数据接口分别采用I2C总线和I2S总线,由于控制总线数据量较少,加之I2C总线时序比较简单,故采用程序控制PIO模拟I2C总线的方式对其进行控制;由于数据总线数据量较大,并且必须保证数据的完整性,本设计采用Verilog硬件描述语言编写了一个Audio控制器,完成采样控制、数据缓存以及与Avalon总线接口等功能。

Audio控制器由有限状态机(FSM)、数据缓存器(FIFO)和总线接口三部分组成,如图2所示。FSM完成WM8731数据读写的控制、FIFO读写与存储状态控制以及总线接口控制。FIFO用来缓冲WM8731采集得到的数据,防止数据丢失,并使系统工作在异步模式,大大提高了CPU的工作效率。总线接口作为桥梁,用以连接NiosⅡ和FIFO。

2.3 数据存储系统的设计

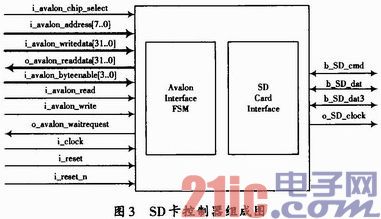

为了实现大容量数据存储,本采集系统选用当下比较流行SD卡作为存储介质。由于SD卡采用的是串行读写方式,时序较为复杂,且其数据量较大,故采用Verilog编写了SD控制器,其结构如图3所示。Avalon Interface FSM与Avalon总线相连接,用来完成控制器与NiosⅡ处理器通信;SD Card Interface与SD卡相连,完成数据的串/并转换和时序控制。

3 软件程序设计

本采集系统软件在Nios EDS环境下进行开发,由于程序中只有一个线程,结构比较简单,故并未采用操作系统。主程序在完成各个模块初始化后进入等待状态,GPS的串口数据、PPS触发信号和按键触发信号采用中断形式,利用中断服务子函数完成各项功能。

3.1 时间信息的解析

由于GPS接收机M12MT具有多种数据输出格式,其中时间格式默认为为格林威治标准时间,故为了保证数据解析的正确性,在系统启动后首先对GPS接收机进行初始化,使其时区设定为GMT+8,每秒钟串口输出一组数据,格式采用@@Eq形式。

由于UART控制器每收到1个字节即产生一个中断,故NiosⅡ处理器首先需要对接收到的数据进行缓存,当收到5个字节后判断是否是报头,如果是报头就继续接收,否则计数器清零并重新进行缓冲。在报头解析正确后,处理器将所有报文依次接收并存储到缓冲区中,缓冲区中的前18位即是时间数据,其格式为mm,dd,yy,hh,mm,ss。

需要特别说明的有两点:第一,由于每一秒的PPS信号早于串口数据的输出,故处理器需要对接收到的时间加1 s,而后利用下一个PPS信号进行触发;第二,GPS接收机在锁定3颗以上卫星时时间数据才具有可靠性,故需要判断报文中的fix标志位,如果fix位是1,这表明卫星已锁定,时间信息可靠,PPS信号可以作为触发信号。

3.2 采集数据的封装

Audio控制器输出的数据是按照采样时刻先后顺序生成的一系列二进制数值点,为了加入起始时刻的时间标志,同时便于评估系统进行后续处理,本录取系统对采样起始时刻和采样数据进行封装。首先将采样数据封装成WAV文件格式,加入相应的格式标志、采样率、采样精度、声道数、数据长度等信息,然后再在WAV文件的前面加入二进制的时间信息形成DAT格式文件。评估系统通过DAT文件中的时间信息和WAV文件中的采样率等信息即可计算出每个采样点的绝对时间。

3.3 文件系统的引用

为了提高SD卡存储的兼容性,便于通用计算机对SD卡的写入和读取,本录取系统利用FAT文件系统对SD卡进行读写操作。由于处理器中没有使用操作系统,故需要自己移植文件系统和编写底层驱动函数。

本录取系统中的文件系统采用层次结构设计,共分为3层,即硬件描述层(HAL)、功能层和应用层。硬件描述层完成SD卡检测、控制命令的写入、数据的读写等功能;功能层完成块数据的读写、查找、替换等功能;应用层完成格式化、文件建立与删除、文件写入与读出等功能。主函数调用应用层的功能函数即可完成对SD卡的文件操作。

4 结论

本文介绍了一种利用SOPC技术在FPGA平台上实现带有时标的嵌入式语言信号录取系统,不但论述了录取系统的结构组成与工作原理,而且对GPS控制器、Audio控制器、SD卡控制器等硬件设计和GPS时间解析、采集数据的封装、文件系统的引用等软件编写进行了详细的介绍。经实际使用验证,本录取系统能够在GPS时间触发下完成语音信号的录取,录取得到的数据带有时标信息,能够满足语音电台抗干扰客观评估系统的技术要求。

畅学电子

畅学电子