电阻抗成像(Electrical Impedance Tomography,EIT)技术是一种廉价的无损伤探测技术,不使用放射源,对人体无害,可作为对患者进行长期、连续监护的医学监护设备.

在医学领域,考虑到患者的安全,激励信号源的电流应小于5 mA;不同人体组织的阻抗随频率变化的特性不同,因此要求激励信号源可以工作在单频、多频或扫频模式下,频率范围为10 kHz~1MHz。激励信号的波动应小于ADC(Analog to Digital Convertor)的1LSB(Least significant bit,最低有效位),即当数据采集系统采用12 bit ADC时,激励信号源DAC(Digital to Analog Covertor)的精度应高于12 bit。目前,EIT硬件系统常采用两种方法来构造正弦信号发生器。

(1)选择具有片内波形表ROM 和DAC的DDS(Direct Digital Synthesizer,直接数字合成)集成芯片,通过相位累加器的输出对存储在ROM中正弦波的幅度值做查表运算,得到的数字量由DAC产生正弦波。DDS技术具有频率、幅度和相位调节方便,输出频率范围宽的特点。如AD7008,具有32 bit相位累加器、SIN/COS查找表和10 bitDAC,其信噪比为50 dB。

(2)组合电路或小规模的CPLD/FPGA结合外部DAC实现DDS的功能。其波形表可以修改,因而能产生任意波形的信号。

ROM 的容量限制了采样点数,制约了信号源精度提高.本文采用先查表,并用泰勒级数对正弦波插值的方法,使输出的幅度值不再局限于ROM 中存储的数据,可有效的提高信号源精度。

1 系统设计

1.1 泰勒级数插值的原理

目前,FPGA芯片除了丰富的可编程逻辑资源外,还扩充了ASIC型乘法器等特殊功能模块。泰勒级数插值正是利用了FPGA内的乘法器资源,采用先查表然后用泰勒级数插值的方法,通过流水线式运算在每个时钟都得到一个插值数据,从而输出的数据不再局限于波形表中的存储的数据,使正弦波更加光滑,其原理如图1。

ROM 中存储了一个周期内N个等间隔的θi幅值sin(θi),对未存储在ROM 中的θ,由泰勒级数插值得到,如式(1)所示。

sin(θ)≈ sin(θi)+ cos(θi)·(θ-θi)-1/2sin(θi)·(θ-θi)2(1)

在FPGA中,通过流水线式的查表、乘加运算进行泰勒级数插值,各级运算互不影响,数据可随时输出。

1.2 硬件结构

基于FPGA的信号源主要由三部分构成:FPGA,14 bit高速DAC AD9754及用于控制幅值的8bit DAC AD7524,如图2所示。

上位机通过串口将信号的频率、初始相位和幅值信息送至FPGA。FPGA输出数字量由高速DAC转换为正弦波;同时,通过辅助DAC控制幅值。输出波形再经滤波电路滤除谐波分量,获得需要的波形。

1.2.1 基于FPGA的DDS模块

泰勒级数插值需要大量乘法运算,小规模CPLD/FPGA往往不提供专门的乘法器模块.作者选择的Xilinx公司XC3S200 FPGA芯片有12个ASIC型嵌入式18×18 bit二进制乘法器模块。结构上,每个乘法器配备一个Block RAM,保证了数据处理的效率,可以实现18位有符号数的高速乘法运算。

DDS模块采用Xilinx公司的IP核(Intellectual Property Core,知识产权核)在FPGA 内构造。IP核根据Xilinx的FPGA器件特点和结构设计,直接用Xilinx底层硬件原语描述,可充分发挥FPGA的功能,保证速度和可靠性。该DDS模块最多支持16通道,各通道的频率和初始相位可通过相位增量(PINC)或相位偏移量(POFF)分别控制;WE为高时,由DATA分别写入POFF和PINC控制字。POFF和PINC与初始相位、输出频率的关系分别为(相位累加器为32位),

SINE和COSINE端分别输出正弦和余弦波。单通道DDS的ModelSim 6.0仿真波形如图3所示。图中,SINE与COSINE的相位相差90°,频率可由WE和DATA写入PINC控制。

1.2.2 数模转换电路

人体电阻抗成像系统激励信号源的频率动态范围较大,要求数模转换电路有较高的无杂散动态范围(SNFR)。系统选择了14位的AD9754,其时钟频率为125 MHz,波形建立时间35 ns。当输出频率为5 MHz时,AD9754的SNFR为83 dBc。

激励信号源应具有幅值调节功能。本文中,AD9754的参考电压Vref由8位的辅助DAC(AD7524)提供,如图4示。AD9754满幅输出电流为IOUTFS=32×Vref/Rset,其中Rset为定值限流电阻。通过AD7524可以做到激励电流幅值256级可调,适应不同的测量对象和激励方式。

为了使系统稳定的工作,可靠的时钟是非常关键的。FPGA对时钟进行倍频/分频、消抖后再提供给DAC,可以保证DAC的时钟占空比为50%且不存在相位偏移。

1.3 多频率成分信号源

IP核技术的本质特征是功能模块的可复用性。因此,不改动外部电路,即可产生多种频率成分的波形。本文实现了具有三种频率成分的信号源。在FPGA内把三个不同频率DDS模块的输出相加,再进行数模转换,即可得到具有三种频率成分的波形。三个频率分别为100 kHz,400 kHz和1 MHz,ModelSim仿真的波形如图5所示。

1.4 上位机接口

本系统中,FPGA通过RS232接口与PC机通信,用VHDL语言编程在FPGA内实现UART(通用异步收发器)模块;UART通过MAX3232芯片转换成RS232接口的电平标准与PC机通信。使用时,由上位机发送频率、初始相位和幅值的控制字给FPGA,单频信号源的频率、初始相位和幅值分别用8位控制。这样可用频率数为256个;最低有效位可设定,当为6 kHz时,可用频率为6×NkHz(N=0,1,……255);最高频率为1530 kHz。DDS的初始相位由8位控制,可以为M×1.41°(M=0,1,……255);同样,通过8位控制字实现幅值的256级可调。

2 结果

按以上方法设计的激励信号源达到了预期的性能指标。将其特征和相关性能与AD7008进行了比较,见表1。

表1 本信号源与AD7008比较

项目

本信号源

AD7008

时钟

0-125MHz

20或50MHz

DDS精度

20位

10位

DAC精度

14位

10位

数据产生方式

先查表再插值

简单查表

信噪比

78dB

50dB

可否多频率

是

否

AD7008内置ROM存储有212(=4096)个10位二进制数,即32位相位累加器只使用了高12位对ROM进行查表运算。与此不同,本文采用先查表后插值的方法,虽然ROM 内的采样点数有限,但DDS输出的数据不局限于ROM 内存储的数据,且精度高达20位。综合考虑系统精度和成本因素,作者选择了14位的AD9754。插值法的使用和DAC精度的提高使输出的正弦波比AD7008的波形更加光滑,如图6。

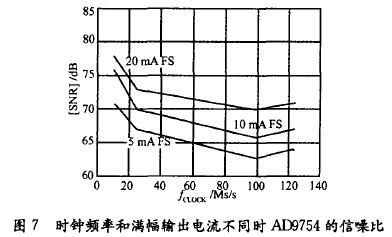

在理想状况下,DAC的噪声只包含量化噪声,信噪比为[SNR]=(6.02×B+1.76)dB,其中B为DAC的位数.对于AD9754,理想情况下的信噪比为86 dB;实际信噪比可以达到78 dB(图7),而AD7008的信噪比只有50 dB。分析可知,信号源输出波形的最大谐波出现在(fclk/fout-1)倍基频处,因此,采用低通滤波器滤除高次谐波.当fout=1MHz时,最大谐波出现在49 MHz(时钟频率为50MHz)。滤除高次谐波后,系统信噪比还可进一步提高。目前,系统稳定工作在50 MHz,而ISE 7.1的仿真结果显示,DDS最高工作频率可以达到153.046MHz。当输出频率达到6 MHz时,波形仍比较理想。根据人体阻抗成像系统的需要,把系统的输出频率范围设定为0~1.5 MHz。

3 结论

综上所述,本文设计并实现了一种基于FPGA的14位高精度激励信号源,信噪比为78 dB;不需改动外围电路,即可工作在单频、多频和扫频模式下;频率、初始相位及幅值调节方便,可以满足不同激励模式下人体电阻抗成像系统的需要。