静态随机存储器(static RAM),简称SRAM。在电子设备中,常见的存储器有SRAM(静态随机访问存储器)、FLASH(闪速存储器)、DRAM(动态存储器)等。其中不同的存储器有不同的特性,SRAM无需刷新电路即能保存它内部存储的数据。而DRAM每隔一段时间,要刷新充电一次,否则内部的数据即会消失。与SDRAM相比,SRAM不需要时钟信号,即可保持数据不丢失。

1、VDMS16M32芯片介绍

VDSR16M32是一款工作电压3.3V,16Mbit,32位数据总线的立体封装SRAM模块芯片,由4个256K x 16bit的SRAM芯片堆叠而成。整个模块采用立体封装堆叠技术,它们之间的互相连接线非常短,寄生电容小。

1.1 芯片的内部功能结构和外部引脚

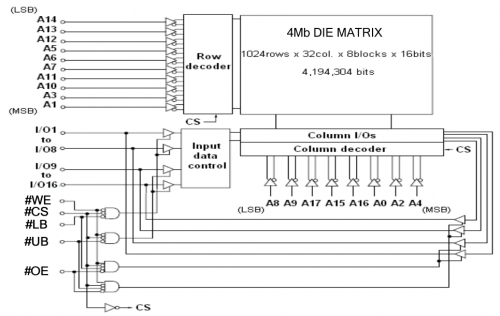

图1是立体封装的大容量芯片VDSR16M32中每一片SRAM的内部结构和功能框图,由MEMORY存储矩形阵列,列译码器、行译码器、数据控制和控制逻辑等部分组成。

图1 VDSR16M32中SRAM的内部功能结构框图

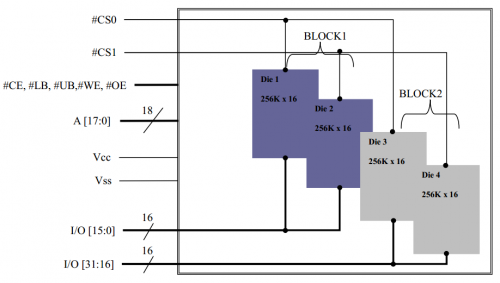

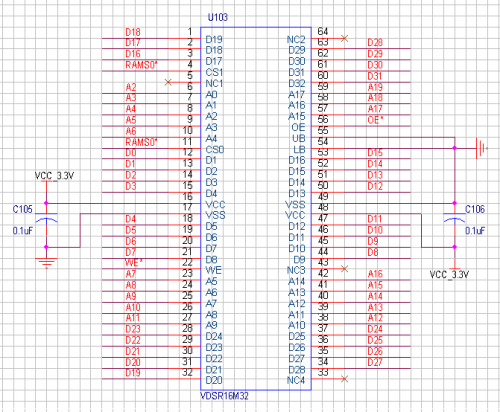

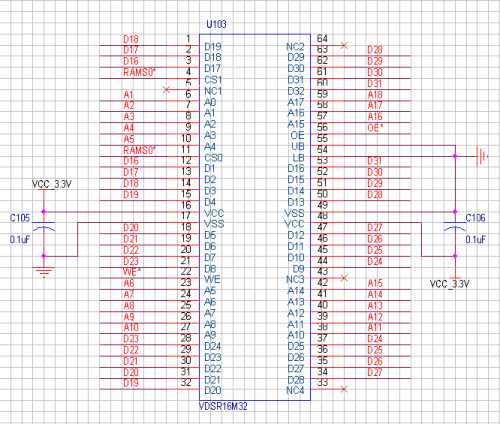

图2是立体封装的大容量存储芯片VDSR16M32的内部结构和功能框图,图3是VDSR16M32的外部引脚分布图,其中A【0:17】是地址输入信号引脚,#CS0、#CS1是芯片里面BLOCK1和BLOCK2的选择引脚,#OE是芯片的输出启用引脚,#WE是芯片的写入启用引脚,#LB是低16位的选择信号,#UB是高16的选择信号,I/O【0:31】是芯片的数据线,其中数据线D【0:15】为BLOCK1的数据输入输出引脚,数据线D【16:31】为BLOCK2的数据输入输出引脚,VCC为电源引脚,VSS为接地引脚。

图2 立体封装的大容量芯片VDSR16M32的功能结构框图

图3 VDSR16M32的外部引脚分配图

VDSR16M32的引脚的功能如表1所示:

管脚

名称

功能

#CS0

Chip select

Disables or enables memory die1 and 3 operation

#CS1

Chip select

Disables or enables memory die2 and 4 operation

A0-A17

Address

Row/column 18-bit addresses

#WE

Write enable

Enables write operation common to all dies

#OE

Output enable

Enables data output common to all dies

#UB

Upper byte select

Latches upper bytes addresses common to all dies

#LB

Lower byte select

Latches lower bytes addresses common to all dies

I/O1-I/O32

Data input/output

Data I/O1 to I/O16 activated from dies 1 and 2 and Data I/O16 to I/O32 activated from dies 3 and 4

Vcc/Vss

Power supply/ground

Power and ground for the input/output buffers and core logic.

NC

No connection

This pin is recommended to be left No Connection on the device.

表1 VDSR16M32的引脚的功能

1.2 芯片的主要特性

1、访问周期:最小12ns;

2、不需要时钟信号;

3、兼容TTL电平;

4、数据至少可以保持20年;

5、由两个256K*32bit的块组成;

6、由5片4Mbit SRAM 堆叠而成;

7、2个独立片选#CS0,#CS1; 8、

8、工作电压:3.3V;

9、64脚TSOP封装。

1.3 芯片的操作

芯片VDSR16M32的工作模式和SRAM差不多,都具有读写操作模式,关于芯片VDSR16M32的操作模式的真值表如下图4所示:

图4:VDSR16M32的工作模式的真值表

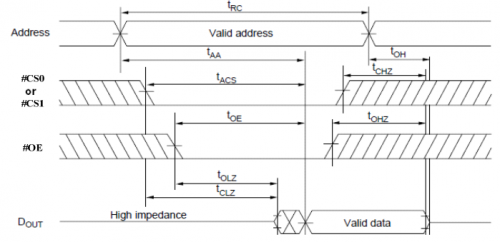

VDSR16M32的读操作非常简单,当片选#CS0或者#CS1和输出启用引脚#OE都为低电平时,芯片进行读操作,即可从芯片读出数据。VDSR16M32芯片的读操作时序图如图5所示:

图5 VDSR16M32芯片的读操作时序图

VDSR16M32芯片的读取操作步骤如下:

1) 通过地址总线把要读取的bit的地址传送到相应的读取地址引脚(这个时候/WE 引脚应该没有激活,所以SRAM 知道它不应该执行写入操作) 。

2) 激活#CS0或者#CS1选择该芯片的BLOCK0或者BLOCK1。

3) 激活#OE引脚让VDSR16M32知道是读取操作。

第三步之后,要读取的数据就会传输到数据总线。

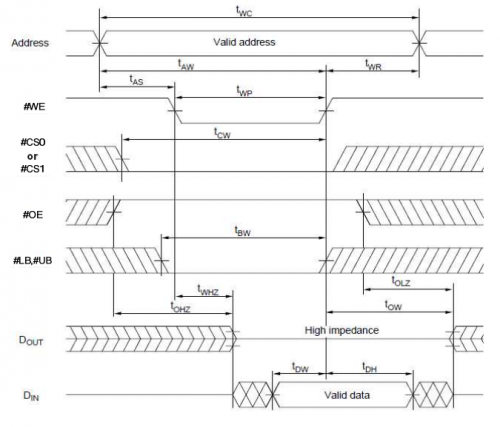

VDSR16M32的写操作同读操作类似,当片选#CS0或者#CS1和写入启用引脚#WE都为低电平时,芯片进行写操作,即可写入数据到芯片中区。VDSR16M32芯片的写操作时序图如图6所示:

图6 VDSR16M32芯片的写操作时序图

VDSR16M32芯片的写入操作步骤如下:

1) 通过地址总线确定要写入信息的位置(确定#OE 引脚没有被激活)。

2) 通过数据总线将要写入的数据传输到I/O引脚

3) 激活#CS0或者#CS1选择该芯片的BLOCK0或者BLOCK1。

4) 激活#WE引脚,通知VDSR16M32芯片知道要开始写入操作。

经过上面的四个步骤之后,需要写入的数据就已经放在了需要写入的地方。

2 VDSR16M32的硬件电路设计

2.1 VDSR16M32与S698-T的电路连接

S698-T是珠海欧比特控制工程股份有限公司面向嵌入式控制领域而研制的一款高性能、高可靠的 SoC 芯片,S698-T芯片的存储器控制器提供了直接访问PROM、I/O空间、SRAM、SDRAM的接口。其中,访问ROM、I/O空间、SRAM时,支持8位、16位和32位三种数据总线宽度,其存取时间参数可配置。下面以S698-T为例介绍SRAM存储器为不同位宽时与MCU的硬件连接方式。

VDSR16M32作为32位存储器时与S698-T微处理器的电路连接图如图7所示,其中Data【31:0】为微处理器S698-T的32位数据线,Address【19:2】是S698-T中28位地址线中的第2位至20位,S698-T在32位总线访问时,地址线从A2开始选址。OE*是S698-T的外部存储器输出使能信号低电平有效。WE*是S698-T的外部存储器写操作使能信号,低电平有效。RAMS0*、RAMS1*是S698-T的SRAM BANK0、BANK1的片选信号,低电平有效。当S698-T进行32位总线进行读写数据操作时,必须同时选择片选#CS0和#CS1。

图7 VDSR16M32作为32位存储器与S698-T的电路连接图

VDSR16M32作为16位存储器时与S698-T微处理器的电路连接图如图8所示,其中Data【31:16】为微处理器S698-T的高16位数据线,S698-T是高数据位有效。Address【18:1】是S698-T中28位地址线中的第1位至18位,S698-T在16位总线访问时,地址线从A1开始选址。OE*是S698-T的外部存储器输出使能信号低电平有效。WE*是S698-T的外部存储器写操作使能信号,低电平有效。RAMS0*、RAMS1*是S698-T的SRAM BANK0、BANK1的片选信号,低电平有效。当S698-T进行数据操作时,选择片选#CS0或者#CS1来选择操作BLOCK0或者BLOCK1,BLOCK。

图8 VDSR16M32作为16位存储器与S698-T的电路连接图

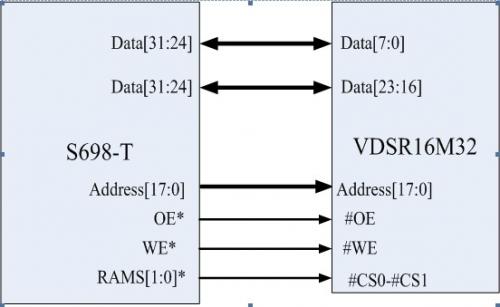

VDSR16M32作为8位数据与S698-T连接时,牺牲了芯片的一半性能,所以不推荐这样使用。VDSR16M32作为8位存储器时与S698-T微处理器的电路连接图如图9所示,其中Data【31:24】为微处理器S698-T的高8位数据线,S698-T是高地址有效。Address【17:0】是S698-T中28位地址线中的低18位,OE*是S698-T的外部存储器输出使能信号低电平有效。WE*是S698-T的外部存储器写操作使能信号,低电平有效。RAMS【1:0】是S698-T的SRAM BANK0-BANK1的片选信号,低电平有效。

图9 VDSR16M32作为8位存储器与S698-T的电路连接图

3.结 语

对于由静态随机存储器(SRAM)堆叠而成的立体封装的大容量存储芯片VDSR16M32,由于拥有32位数据线,两个BLOCK,并且数据位可灵活配置,可满足不同CPU对位宽的要求。同时基于SRAM芯片立体封装存储器缩短了内部信号连接长度、减少了寄生效应,增强了抗干扰能力,可广泛用于车辆、卫星、飞机和空间站等对存储器条件要求高的地方。