当恩智浦半导体开始使用先进的低功率芯片设计技术时,有一件事令其大吃一惊。“某些情况下,在实现阶段出现了两倍的产能下降。”NXP公司设计与技术负责人Herve Menager表示。

从整个行业来看,这并不是一个特例。虽然EDA供应商们一直在为两种竞争性的低功率规范争斗不休,但它们似乎忽略了一个更大的问题:类似多电压设计等低功率技术如此困难,以至于设计人员需要重新考虑整个芯片的设计流程。在最近于加州Monterey举行的电子设计过程(EDP)大会上,Menager和其它芯片设计师详细探讨了这方面的挑战。

EDA供应商们理解设计师所处的两难境地。“产能带来的影响是巨大的。”Cadence设计系统公司Encounter营销副总裁Eric Filseth说,“低功率技术不能单靠版图,这是架构方面的事,涉及验证、实现、测试等整个设计阶段。”

大多数观察人士认为,业界已经确立了诸如门控时钟和多电压阀值(multi-Vt)等一些基本的低功率设计技术,而且它们也得到了现有工具的支持。门控时钟通过限制时钟分配来减少动态功率,多电压阀值设计在非关键性能处使用高电压阀值单元来降低漏电流。

设计师遇到的难题在于怎样利用更先进的多电压技术。在采用多电压供电(multi-Vdd)方法时,一些模块的供电电压要低于其它模块,从而形成电压“孤岛”。这种情况在静态电压时已经非常复杂,而当采用动态电压调整方法在工作期间改变电压值时,会变的更加复杂。

为了降低漏电流,一些设计采用功率选通法并通过多阀值CMOS(MTCMOS)开关关闭不在使用状态的模块。在这里,上电和断电顺序的设计和验证可能会特别复杂。

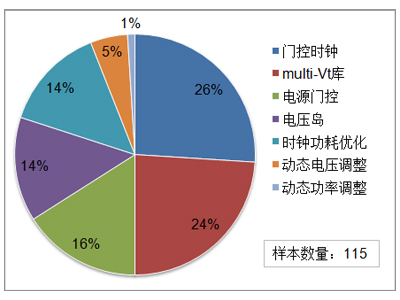

先进的技术也在不断迎头赶上。在2006年设计自动化会议上,由Sequence Design公司撰写的调查报告指出,有26%的受访者表示正在使用门控时钟,另有24%使用的是multi-Vt库(参见图1)。

图1、设计人员正在使用电压岛、电源门控和其他功率控制技巧

“多电压和电源关断等先进技术会影响到整个设计流程。”新思公司RTL综合和低功率产品部营销总监Gal Hasson表示。

设计挑战

Menager在EDP会议上指出,截至目前,NXP已经尝试借助两种方法来解决动态功率问题,分别是通过门控时钟降低功耗,以及减小开关电容。最近,该公司开始使用电压岛和频率调整方法来满足性能和功率要求。

多电压设计通常需要:电平转换器,让信号跨越电源域边界;保持寄存器,在断电时保持状态信息;片上开关,实现加电和断电;隔离单元,在断电时控制输出。这些技术NXP都在使用,但针对电路单元的自动实现和验证的详细意图却非常复杂,Menager表示。

例如,电平转换器引入的版图约束会极大提高CAD工具的复杂性,Menager表示。虽然版图在逻辑上是正确的,但在物理方面却可能出错,他指出。

Menager表示,当隔离钳位二极管用于电源开关时,可能传输不必要的数据,而浮置输入端也可能发生短路。保持寄存器可能需要缓存树对控制信号“常开”,而电源连接不仅容易出错,而且非常耗时,他说。

Menager认为,电压岛可以利用片上开关打开或关闭,但这样做会使电源分配和底层规划变得更为复杂。开关需要合适的尺寸来平衡电流承载能力与面积和漏电流二者之间的关系,有必要使用静态IR压降分析来验证这个尺寸。

在SoC级,全局缓冲策略和电源分布是很复杂的,Menager指出。

低功率设计对可测试设计(DFT)影响很大,Menager指出。在电压岛间插入扫描链会大量增加复杂性。

“我们需要对后端实现具有更少破坏性的灵活解决方案。”Menager说,“重要之处在于捕获,且在早期正确捕获电源网络的意图。”

通用功率格式(CPF)对捕获电源意图至关紧要。据Menager透露,NXP已经使用了Si2的CPF,并发现其极具价值。但在CPF和Accellera的统一功率格式(UPF)之间的标准之争却是个令人头疼的问题。

“好消息是我们终于从无格式发展到有格式,”Menager说,“坏消息却是,我们一下子从一无所有跳跃到有太多选择。”

当时钟变得复杂

飞思卡尔半导体公司也使用多电压技术,其GSM手机的待机电流和工作电流正在以每年大约15%的速度下降,设计经理Milind Padhye表示。Padhye指出,采用多电压设计法后,设计中的未用部分其电源可以被切断;低性能部分可以工作在较低电压下。不过,这样做也存在着成本问题。

“对多电压设计而言时钟是一个最大的挑战。”Padhye表示,“电压促使时钟移位。当时钟开始移位时,时序就会出现混乱。最终可能需要上百个边界条件来优化时序。”

Padhye 认为,为了达到高效的电压分割,需要采用架构分析方法,并且系统必须经过多次验证,包括断电过程中、断电完成后以及上电期间。“假设你创建的某个事务在断 电状态下终止,而且现在芯片也不工作了,”Padhye说,“你如何进行调试?这就好似对一个死者询问‘你能告诉我你是如何死亡的吗’一样。”Padhye宣称,避免1个电源缺陷相当于避免10个功能性缺陷。

针对保持验证,设计人员必须确认状态被正确保存和被正确恢复,而且系统能在上电后正常工作。针对电压和频率变化,设计人员必须验证系统性能状态、电压变化,以及变化期间和变化后的系统操作。

Padhye指出,整个流程能始终支持低功率技术是很重要的。虽然飞思卡尔公司正在使用CPF,但最终还是希望业界能够采用统一的功率格式,Padhye表示。

更高抽象层

TI公司科学家Mahesh Mehendale也赞成在低功率设计中采用系统级方法。他的EDP演讲综述了多标准、多格式视频处理器SoC面临的低功率设计挑战。

据Mehendale透露,TI公司在SoC级的电源管理策略包括:自适应电压调整,可根据工艺和温度最小化电压;动态电源切换,可在不同电源模式间切换以减少漏电流;动态电压和频率缩放,可调整电压和频率来适应性能要求;多电压域;以及静态漏电管理。

Mehendale 指出,技巧在于找到频率与公共集电极电压间的“功率最优化”工作点。较低的Vcc有助于动态和泄漏功率,但如果Vcc下降但是频率保持不变,那么门数量将 会上升,从而有悖于任何功率节省方案。如果在架构级进行选择,优化的MHz/Vcc折衷可驱动对并行和管线机制的需求。

“功耗问题需要在所有抽象级加以解决。”Mehendale说,“其在系统和架构层的影响尤其显著。”

包 括Cadence、新思和Magma在内主要的IC实现工具供应商都表示,他们正在改善对先进的低功率设计技术的支持。今年早些时候,Cadence在 CPF基础上推出了一款低功率设计流程。由Cadence公司开发的这一流程正在推进标准化,它在综合、验证、形式等效性检查、DFT和物理版图方面都有 效融合了功耗意识。

目前Cadence尚未提供的功能是系统级低功率设计。“这是一定要做的事,”Filseth说,“架构和系统级是获得功率节省的主要场合。”

新思公司的所有综合优化功能(包括DFT)都具有“功率意识”,Hasson表示。为了支持多电压设计,新思的综合工具可以确定保持、隔离和电平转换单元。在物理实现方面,新思的电源网络规划工具可以执行电压下降分析,它的版图工具可以正确放置电源开关。

Magma设计自动化公司两年前就提供了一体化的低功率设计流程,Magma公司低功率产品部产品经理Arvind Narayanan表示:“Herve Menager谈到的multi-Vdd流程在系统中是自动实现的。”

供应商们表示,多年来对低功率设计的支持一直是EDA产业的优先考虑对象。“这并不是对现有工具的功能追加,” Filseth认为,“而是对设计流程该如何工作的重新通盘考虑。”