摘要:给出了一种利用电子设计自动化( EDA) 软件对复杂可编程逻辑器件(CPLD) 进行设计以实现8 位发光二极管(LED) 显示驱动器的方法。设计结果表明, 用1 片Lattice 公司的ispLSI1032E(6000 门密度) 最多可以驱动12 位LED 显示器。文中还就如何减少资源进行了探讨,介绍了5 种方法。

发光二极管(LED) 显示驱动器是电路设计中经常使用的部件,例如MAX7219 和PS7219 。这些器件的功能非常多,能满足不同用户的设计需求,但对于许多设计者来说并不需要如此多的功能应用,此时可以借助电子设计自动化( EDA) 技术和复杂可编程逻辑器件(CPLD) 设计专用芯片。

本文给出了一种利用电子设计自动化( EDA) 软件对复杂可编程逻辑器件(CPLD) 进行设计以实现8 位发光二极管(LED) 显示驱动器的方法。设计结果表明,用1 片Lattice 公司的ispLSI1032E(6000 门密度)最多可以驱动12 位LED 显示器。本文还就如何减少资源进行了探讨,介绍了5 种方法。

1 LED 显示驱动器功能

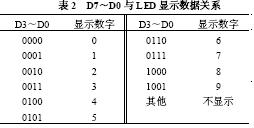

本设计中,LED 显示驱动器采用流行的同步串行外设接口(SPI) ,使之可以方便地与各种常用单片机连接。该驱动器可以同时驱动8 位LED 数字显示器或64 个独立的LED ,还可以对每位数字单独控制、刷新,不需重写整个显示器。串行输入的16 位数据字中包含对某个LED 操作的地址和数据,如表1 和表2 所示。其中,D11~D8 是4 位地址,D7~D0 是8 位数据,D7 用于指示小数点的显示与否,D3~D0 用于确定LED 显示的数字。

2 电路设计

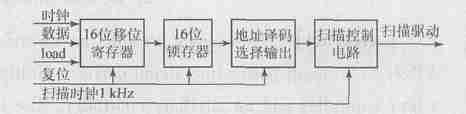

LED 显示驱动器电路组成如图1 所示。它包括4个模块:16 位移位寄存器、16 位锁存器、地址译码选择输出和扫描控制电路。输入信号有5 个:串行输入时钟、串行输入数据、数据装载输入load、扫描时钟和复位信号。电路的输出信号是8 个数据输出和8 个扫描输出,其中数据输出接LED 的8 个输入端,扫描输出接每个LED 的片选端。串行输入数据在时钟上升沿进入16 位移位寄存器,当16 位数据都进入后,装载数据load 的上升沿把16 位数据装入16 位锁存器。接着对16 位接收数据的D11~D8 位进行地址译码,根据译码结果将数据D7~D0 (实际上只是D7 、D3~D0 5位数据) 传给相应的LED 显示。

图1 LED 显示驱动器的电路结构

要达到对每位LED 单独控制的目的,必须使多个LED 共同显示,即当某个LED 显示时,必须不影响前面已显示的位。解决办法是利用锁存器将前1 位或多位锁存,这样需要8 个5 输入的锁存器。这是本电路中需用组合资源最多的地方。

如果采用静态显示输出,需要的输出引脚是64个, IO 资源不够,所以这里采用动态扫描显示的方法。扫描显示每次只选择一个LED ,并送出相应的数据,8个LED 在扫描时钟的作用下,利用状态机的状态循环依次显示。如果扫描速度足够快(1.5 kHz 以上) ,人眼是看不出有闪烁的。所有功能模块均采用硬件描述语言ABEL 编写并进行功能仿真。

需要指出的是,这里实现的功能都是实际中经常用到的,例如显示的数据实际上是带译码方式的。如果用户需要不译码方式,只需将8 位数据不经过译码模块处理直接输出。其他功能例如闪烁可以通过增加模块实现。这一点对于具有在系统可编程能力的CPLD/ FPGA 来说并不困难。

3 实现结果

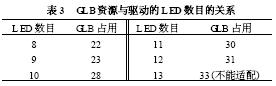

本设计使用的CPLD器件是Lattice 公司的ispLSI1032E ,84 引脚,密度为6 000 个门,32 个通用逻辑模块( GLB) 单元。适配的结果占用了22 个GLB ,最高时钟速率达到65 MHz。如果驱动更多的LED ,则所需资源情况如表3 所示。

CPLD 的工作速度可以适应各种单片机。用CPLD 实现的LED 显示驱动器替代目前市场上的同类产品也有许多可取之处,例如减小电路板体积、功能更紧凑、修改更灵活方便等。

4 讨论

实现电路的功能是可编辑逻辑器件( PLD) 设计人员首先需要考虑的,另外,作为一个有经验的PLD 设计人员来说,还需要掌握如何用最少的资源求得功能的实现,这样设计出来的专用芯片才具有竞争力。减少芯片资源的占用可以采用下列5 种方法:

尽量减少用原理图实现电路。本设计中使用8个将5 位数据锁存的功能部件,如果利用原理图库中的锁存器单元一级级搭起来,最终在适配时需要占用27 个GLB ,比用硬件描述语言多用了5 个。这是因为:综合器在编译硬件描述语言时执行了逻辑优化等操作,而原理图则没有相应的综合器进行编译与优化。

不要让when-else 语句嵌套。when 语句可以使编程简洁明了,但每个when-else 语句都是与实际的数据选择器对应的。嵌套的层级越多,所需的电路结构越复杂。

用one-hot 编码方式减少组合电路资源。one-hot (1 位热位编码) 是指将状态图的每个状态在编码时对应一个触发器。一般扫描电路设计都由计数器和译码器组成,例如这里就可以让计数器进行模8 计数,在每个计数值输出数据和片选信号,这样做使译码电路非常复杂,相应的组合资源耗费较多。而利用状态图代替计数器,并采用one-hot 可以大大减少组合资源的占用。本设计中,扫描模块用一般计数器加译码器结构时适配结果占用25 个GLB ,而利用状态图加one-hot 编码则只需使用22 个GLB。

选用CPLD 器件做逻辑控制更合适。CPLD的组合资源非常丰富,当实现控制逻辑电路时选用CPLD 比FPGA 更合适,效率更高。Lattice 公司是世界上CPLD器件规模最大的公司,其CPLD产品的内部“与或”阵列结构使其可以提供丰富的组合资源。本设计用一片ispLSI1032E 最多可实现12 个LED 驱动。

利用软件设置编译参数,寻找最佳结果。精通EDA 软件的使用对于更好地完成设计任务是非常有帮助的。本设计中采用的软件是ispDesignEXPERT ,该软件可以对适配过程进行一些参数设置。例如可以设定综合策略为资源、速度、不优化3 种。至于何种参数对设计有利,需要设计者根据实际情况通盘考虑。

需要指出的是,本设计只从逻辑功能上实现8 位LED 驱动器,并没有考虑对具体LED 的驱动能力,实际电路中通常采用缓冲驱动器完成该功能。