基于PowerPC 的嵌入式系统在网络通信应用方面具有不可替代的优势, 论文基于Freescale 公司的MPC8360E PowerQUICCII Pro 处理器设计多网口嵌入式终端系统,实现系统启动、网络数据交换和存储等功能。系统由MPC8360E 基本系统、电源模块、存储模块和网络接口模块及UART 接口、编程接口等模块组成。论文针对PowerPC 控制器及网络接口芯片的抗干扰要求,讨论了电源电路的抗干扰设计、重要信号线的阻抗匹配、未使用信号的合理处理及PCB 的抗干扰处理等关键问题。经测试该系统能够可靠地工作,完成网络通信功能。

1 引言

PowerPC 处理器性能好,稳定性强,集成度高。最新的PowerPC处理器集成了具有通信处理功能的通信引擎(QUICC Engine)技术,在网络通信领域得到了广泛应用。

为满足多个网络产品数据汇接的特殊需要, 本文设计一套多网口嵌入式终端系统, 具有多个网络端口间数据交换和存储的功能。

系统基于Freescale 的PowerPC 处理器MPC8360E 设计,包括MPC8360E 基本系统、电源模块、存储模块和网络接口模块及UART 接口、编程接口。

MPC8360E 处理器首次采用QUICC Engine 技术,具有8 个通用的通信处理器(Unified Communication Controller,UCC),支持广泛的通信接口,为网络、通信的开发提供了一个高性价比、高集成控制的处理器解决方案。

论文讨论了基于MPC8360E 的多网口嵌入式终端系统设计方案及系统框图,重点讨论了系统设计中的抗干扰措施,给出了电源抗干扰电路、PowerPC 及网络芯片特殊信号处理等关键的抗干扰电路设计, 并介绍了分层与布局、BGA 走线、等长走线、蛇形走线、差分走线等抗干扰印制电路板(PCB)设计方法。

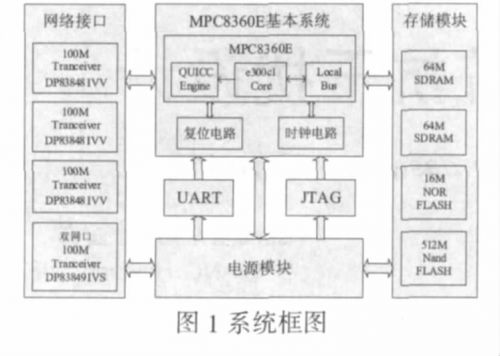

2 基于MPC8360E 的多网口嵌入式终端系统框图

基于MPC8360E 的多网口嵌入式系统具有五个百兆网络接口,能够实现系统启动、网络设备管理及多网络端口的数据传输控制。如图1 所示,主要包括MPC8360E 基本系统、电源模块、存储模块和网络接口模块及UART 接口、编程接口几部分。在MPC8360E 的主控下,几部分协调工作,实现网络数据的交换和存储等功能。

MPC8360E 基本系统提供MPC8360E 正常复位及启动需要的基本信号。MPC8360E 基于增强的e300c1 内核,提供了丰富的系统接口, 如支持general -purpose chip -select machine(GPCM),synchronous DRAM (SDRAM) machine,user -programmablemachines (UPM) 三种接口的Local Bus Controller(LBC)。此外它还使用了QUICC Engine 技术,配备了两个速率可以高达500MHz 的RISC 核心,提供了集成的多协议处理和互通技术,使得MPC8360E 的通信处理功能更加强大。

电源模块负责给整个系统供电, 提供PowerPC 芯片及外围电路需要的3.3V 和1.2V 两种电压。

存储模块用来存储系统启动代码、Linux 内核镜像和网络通信中的数据等, 其包括两片64M SDRAM, 一片16M NORFLASH 和一片512M NAND FLASH.其中,SDRAM 提供程序的运行空间;NOR FLASH 用来存储U-Boot、Linux 内核、文件系统等;NAND FLASH 主要用来存储网络通信中的数据。

系统中通过芯片DP83848IVV,DP83849IVS 与MPC8360E的UCC、网络隔离器的连接提供了五个RJ45 接口,以满足嵌入式终端系统多个网口的需求。DP83848IVV 和DP83849IVS 分别是单端口和双端口以太网物理层收发器,支持100Mbps 全双工工作方式,适用于高速网络互联设备。

JTAG 和UART 接口系统用于调试系统,打印系统调试信息或者其他有用信息。

3 抗干扰电路设计

高频嵌入式系统电路的抗干扰处理措施是影响系统能否正常工作的关键, 电源电路的抗干扰处理、重要信号的阻抗匹配、未使用信号的合理处理,都是确保系统正常工作的关键。本系统设计中,着重研究了电源电路的抗干扰处理、重要信号的阻抗匹配、未使用信号管脚的处理等抗干扰电路设计的关键问题。

3.1 电源电路抗干扰处理

提高电源的抗干扰性是保证系统可靠性的关键问题之一。

系统除了要对输入电源进行稳压外还要采取以下措施: ⑴在每个集成电路的电源与地之间加上高频滤波电容和几十微法到几百微法的大电容器。这些电容既可以旁路掉该电路的高频噪声,又可以滤除纹波,避免电流突变引起电压的波动,从而给电路提供稳定的最佳电压。⑵根据芯片的要求对不同的电源进行特殊相应的处理。

系统所需要的3.3V 和1.2V 电源上都并接了0.1μF、0.01μF 的高频滤波电容器和220μF 的大电容,它们可以有效地抑制在电源线上传导的高频干扰, 克服干扰信号对系统工作的影响,还可以储存能量,给元器件提供稳定的最佳电压。随着应用场合和芯片的不同,电源电路的要求也会有所区别,实际应用中要注意根据具体要求采取相应的设计方案。如MPC8360E 中各个PowerQuicc II Pro PLL 电路不能直接由电源引脚VDD 供电,而是要独立供电。每个PowerQuicc II Pro PLL 都要由它所对应的独立于VDD 的电源引脚AVDDn(n=1,2,3,4,5,6)供电,并且每个AVDDn(n=1,2,3,4,5,6)引脚还要有独立的低通滤波电路。通过这些滤波电路滤除频率在500kHz-10MHz 的噪声, 降低PLL彼此间的噪声干扰。

3.2 重要信号线的阻抗匹配

高速系统设计中信号传输线上阻抗匹配是有效地减小信号反射,提高信号质量的重要措施。一般情况下,对芯片的控制信号、时钟信号等关键信号,采取在尽量靠近这些信号源端的位置上串行接入一个电阻的措施,以减少二次反射,增强信号的完整性。

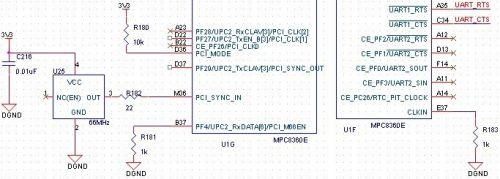

图2 串联端接阻抗匹配电路

本系统中,MPC8360E 的时钟信号线对系统工作具有重要影响,以图2 为例,在传输线上靠近时钟信号源端MPC8360E 位置处串联了22Ω 的小电阻,实现了串联端接阻抗匹配,减小了过冲和振铃,降低了高频成分,增强了电磁兼容性,同时也有利于延长器件的使用寿命。此外,电路中对MPC8360E 的读写控制信号线及某些芯片的地址线等信号线也采取了阻抗匹配处理。

3.3 未使用的重要信号的特殊处理

电路的输入引脚一般都不悬空, 尤其是CMOS 电路的输入引脚绝对不能悬空,否则可能会使栅极因感应静电而击穿,也可能会因受到外界噪声的干扰而破坏电路的正常逻辑关系。

在系统设计时, 对于MPC8360E 芯片的一些重要的不可以悬空的引脚进行了上拉或下拉的处理。

以图3 为例,MPC8360E 有两个时钟输入CLKIN 和PCI_CLK(PCI_SYNC_IN),当系统工作在PCI 缺省模式时,(本系统采用的工作模式), 时钟信号通过PCI_CLK 输入, 并不需要CLKIN.但是引脚CLKIN 不能悬空,要通过1K 电阻连接到地。

再如PCI 信号M66EN 作为输入引脚也不能悬空,可以上拉到固定电平,也可以下拉到地,系统中选用下拉到地的方式。

图3 未使用的重要信号的特殊处理

3.4 网络芯片的抗干扰处理

网络芯片DP83848IVV 和DP83849IVS 都含有内置稳压器,其电源反馈供电电路要正确处理。每个内置稳压器有电源反馈输入引脚和电源反馈输出引脚,要确保其正确工作,必须将电源反馈输入引脚连接到电源反馈输出引脚, 而且还要在靠近各个电源反馈输入引脚处分别并接一个0.1μF 的小电容, 以及在靠近电源反馈输出引脚处并接一个0.1μF 的小电容和一个10μF的钽电容。

4 抗干扰PCB 设计

高速电路系统PCB 设计的好坏严重影响了系统的抗干扰能力, 干扰严重的时候会造成系统无法正常工作。在进行PCB设计时,分别考虑了系统分层与布局、特殊布线及电源平面地平面处理等关键问题。

4.1 分层与布局

确定电路板的布线层数、电源层数以及它们之间的相对排布位置对PCB 设计至关重要,成功解决这些问题,不但可以得到一个好的叠层结构, 还可以更好地防范大多数信号整体问题和电磁兼容性(EMC)问题。多网口嵌入式终端系统,采用了六层叠层结构,其中布线层有四层,电源层和地层各有一层,并且选择将电源层和地层分别放在第2 层和第5 层, 以更加方便地控制信号的阻抗。

多网口终端系统的元件布局遵循信号流向原则, 把同类元器件按相同的方向摆放原则和尽可能地使互连线最短原则等一般原则,同时它的布局还注意了以下几个方面:

⑴电源的去耦电容遵循就近原则, 即每个电源的去耦电容尽量挨着该电源引脚摆放。

⑵芯片MPC8360E 是BGA 封装,布局时与该芯片相关的旁路电容、时钟终端RC 电路、阻尼电阻等小零件要靠近芯片摆放。

⑶网络芯片内置稳压器的滤波电容要特殊放置: 在靠近各个电源反馈输入和输出引脚处均放置一个0.1μF 的小电容,另外靠近电源反馈输出引脚处还要放置一个10μF 的钽电容。

4.2 布线策略

本系统的PCB 设计在遵循45°拐角布线、相邻层垂直布线等一般原则基础上,使用了一些特殊的布线技巧,以减少布线对系统的可靠性产生的不利影响。

4.2.1 BGA 走线

芯片MPC8360E 是BGA 封装,系统中的高频信号大都是从此封装拉出的,为了使BGA 自身信号的干扰降至最低,布线遵循BGA 芯片自身的走线原则。①BGA 封装的芯片MPC8360E扇出前先将芯片由中心以十字划分,过孔分别朝左上、左下、右上、右下方向打在芯片引脚与引脚正中间。如果走线需要,过孔可以从表面层拉出之后再打, 需要注意的是信号线不能在内部回转,要以辐射形态向外拉出。②当旁路电容和芯片MPC8360E在同一面时,走线直接从芯片引脚接至旁路电容,再由旁路电容拉出打过孔到电源平面。③当旁路电容与芯片MPC8360E 不同面时,即旁路电容在底层时,它与芯片MPC8360E 临近的电源、地引脚共享同一个过孔,且线长不超过100mil.④电源线宽、地线宽和时钟信号的线宽大于一般信号的线宽。

4.2.2 等长布线和蛇形布线

有些数据信号或者地址信号对实际走线长度十分敏感,如果它们的长度不匹配就会引起信号的不同步, 从而影响系统的正常工作。在布此类信号线时一般通过采用等长布线的技巧达到信号线长度匹配的要求。本系统中, ①通过等长布线, 芯片MPC8360E 的引脚LSYNC_IN 到引脚LSYNC_OUT 的长度等同于MPC8360E 到SDRAM 的长度,实现了同频同相。②系统中用了两片SDRAM 芯片MT48LC32M16A2,在布线时也采取了等长布线的策略。其中时钟线长度控制在2567±25mil;控制信号线以及地址线和时钟线等长,且线长误差不超过±100mil;数据线尽量和时钟线,地址线以及控制线等长但长度不长于这些线。

等长布线往往需要在规定的空间里增加布线的长度, 这时不可避免的要用到蛇形走线的技巧。如,系统通过蛇形走线增加SDRAM 中某些数据线和时钟线的长度,以实现两片SDRAM 数据线之间和时钟线之间的等长。这样做不但减少了电磁辐射,也调节了延时以满足系统的时序设计要求, 从而使得系统更加可靠。

4.2.3 差分布线

网络收发芯片DP83848IVV,DP83849IVS 中存在差分信号,如TD±,RD±,这些成对的信号在布线时要采用差分布线。一般来说,差分对信号的走线要在同一布线层(side-by-side),它们长度相同并且尽量保持平行, 这样既可以保证两个差分信号时刻保持相反极性, 又可避免出现两线忽远忽近引起差分阻抗不一致的情况, 从而达到减少共模分量和减少反射的目的, 更有利于解决信号完整性(signal integrity)问题。以图4 为例,系统PCB设计中,在PCB 绘图软件中对差分信号的规则进行了设置,以达到差分布线等长等距的要求,从而提高了系统的抗干扰能力,有效地抑制了EMI,还使得时序定位更加准确。

4.3 电源平面(线)和地平面(线)的处理

六层电路板中其中一层全部用铜箔做成地平面, 有效地解决了高频电路的信号完整性问题。另外,电源使用整层平面,然后根据系统电压的大小对电源平面进行分割, 以减少电压之间的相互干扰。其中,在进行电源分割时,尽量使芯片的电源引脚就近打孔后可以直接到达电源平面。

增加信号层中的电源线和地线宽度, 使得它们大于一般信号的线宽。同时,电源线、地线的走向要和数据传递的方向一致,以增强系统的抗噪声能力,从而使系统更加可靠。

5 结论

从系统电路原理设计到PCB 绘制,采取合理的抗干扰措施,是高速电路设计的关键。本文基于PowerPC 实现嵌入式多网络终端,硬件设计的可靠性更是不可忽视的问题。论文解决了电源电路的抗干扰、重要信号线的阻抗匹配、网络接口电路的抗干扰及PCB 的抗干扰等关键问题,按照论文的设计原则设计的系统样板如图5 所示。该系统能够可靠地工作, 完成数据交换和存储功能。