摘要:

随着电子设计领域的高速发展,产品越来越小,速率越来越高,信号完整性越来越成为一个硬件工程师需要考虑的问题。串扰,阻抗匹配等词汇也成为了硬件工程师的口头禅。电路板尺寸变小,成本要求提高,电路板层数变少,使得布线密度越来越大,串扰的问题也就越发严重。本文从3W规则,串扰理论,仿真验证几个方面对真实世界中的串扰控制进行量化分析。

引言:

信号频率升高,上升沿越来越陡,电路板尺寸越来越小,成本要求越来越高,是当今电子设计的趋势。尤其在消费类电子产品上,基本都是四层或者六层板,除去必要的电源地平面,其他层密密麻麻全走着信号。串扰也成为了一个最常见的问题。串扰的危害巨大,直接影响着信号是否能够正确的接收。对于串扰,业内通常有3W规则的说法,只要走线没有达到3W,就会引起一些硬件工程师的恐慌。是否一定要3W?如何去尽量的避免串扰?对串扰有一个量化的概念将会让我们的设计更加有把握。

1.3W规则

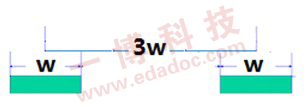

在PCB设计中为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持大部分电场不互相干扰,这就是3W规则。如(图1)所示。

<ignore_js_op>

图1

3W规则只是一个笼统的规则,在实际的PCB设计中,若死板地按照3W规则来设计会导致成本的增加。

无法满足3W规则时,可以通过对串扰的量化的理解,来改变一些其他的参数保持信号完整性。

2.串扰理论

当信号沿传输线传播时,信号路径和返回路径之间将产生电力线;围绕在信号路径和返回路径周围也有磁力线圈。这些场并不是被封闭在信号路径和返回路径之间的空间内。相反,它们会延伸到周围的空间。我们把这些延伸出去的场称为边缘场。这些边缘场将会通过互容与互感转化为另一条线上的能量。而串扰的本质,其实就是传输线之间的互容与互感。

2.1 容性耦合

容性耦合示意图如下(图2):

<ignore_js_op>

图2

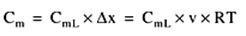

容性耦合电流为:

<ignore_js_op> 式1

式1

其中Cm为一个上升沿所覆盖的传输线长度的电感,V为信号幅值。

<ignore_js_op> 式2

式2

其中Cml为分布电容(单位长度电容),v为传输速度,RT为上升时间。

<ignore_js_op> 式3

式3

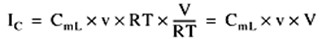

2.2 感性耦合

感性耦合示意图如下(图3):

<ignore_js_op>

图3

感性耦合电压为:

<ignore_js_op> 式4

式4

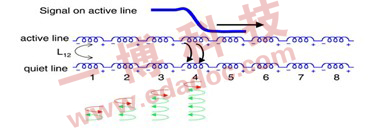

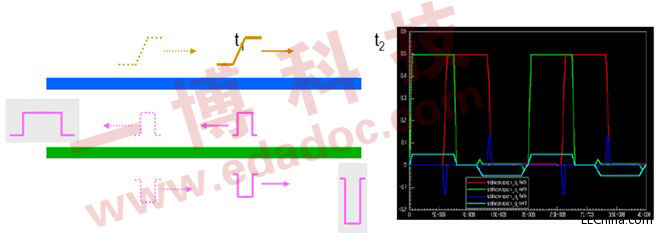

2.3 近端串扰与远端串扰

由静态线耦合到动态线上的串扰分成两部分,一部分往与信号方向相同,传至接收端方向,我们把它叫做远端串扰或者前向串扰。另一部分与信号方向相反,传至发送端方向,我们把它叫做近端串扰或者后向串扰。

如下图(图4)所示:

<ignore_js_op>

图4

后向串扰幅值不增加,持续时间随着耦合长度增加而增加。前向串扰时间与信号同时传播,幅度随着耦合长度增加而增加,最终达到饱和。

2.4 饱和时间

当一个完整的上升(下降)延完成时,近端串扰饱和。近端串扰饱和时间为信号的上升时间RT,所以近端串扰饱和长度为RT*v。

理想条件下,微带线的远端串扰在幅值达到信号幅值的1/2时饱和。带状线没有远端串扰。

这个RT*V大概是个什么样的概念呢?我们知道,在普通的FR4材料中,我们的V大约为6in/ns。通常我们DDR3跑1066Gbp/s信号的上升时间在0.1ns左右(可以根据上升时间等于十分之一的信号周期来估算信号的上升时间)。也就是说,当耦合长度达到600mil时,噪声才会饱和。在实际走线中,由于一些容性因素,会将上升时间拉的更长。在耦合长度达到饱和长度之前,噪声大小与耦合长度成正比。继续以DDR3,1066Gbp/s的信号为例,若达到饱和长度时的噪声为80mV,则在300mil时的耦合噪声为40mV。

2.5 串扰与阻抗

我们通常控制阻抗的方法是改变走线与参考平面之间的距离,或者调整线宽。若线间距与线宽比例保持不变的话。有一个很有趣的事实,为了控制阻抗,我们如果减小了走线与参考平面之间的距离的话,必须同时减小线宽。减小与平面之间的间距串扰将减小,而减小线宽串扰将增加。不管层叠线宽介电常数如何调整,串扰和阻抗正相关。阻抗变小,串扰也变小,阻抗变大串扰也将变大。

本文所有的量化数据全部基于阻抗为50ohms时的仿真,并且在任何时候,只要阻抗不变,串扰都可以通过这些数据去做出估值。