0引言

图像处理技术是信息科学中近十年来发展最为迅速的学科之一。目前,数字图像处理技术巳被广泛应用于航空航天、通信、医学及工业生产等领域中。但是,如果单纯使用现成的专用视频图像处理芯片,根本无法设计出具有自主知识产权的产品。随着网络技术、大规模,超太规模集成电路(ASIC)以及现场可编程门阵列(FPGA)的发展,它们在图像领域的应用越来越广泛,同时,图像处理设计也正朝着速度快、容量大、体积小、重量轻的方向发展,这也为图像处理系统的设计和实现提供了新的方法和思路。

1系统功能

本系统的功能图如图1所示,其结构图如图2所示。它以内嵌Nios软核的FPGA,低级,高级为核心,并将图像采集芯片和存储器等外围设备芯片嵌入到系统上,从而实现图像的采集处理和显示,并将处理后的数据通过调制解词器经由PSTN网络发送到接收端(监控中心),以便在监控中心能够使用在PC上编写的上位机程序将处理后的图像显示出来。

2图像处理的实现

21图像采集模块

图像采集模块采用富士通公司生产的一款375x293(10万)像素(即CIF恪式)的CMOS图像传感器MV86S02,该芯片在片内集成了色彩信号处理器。这种将CMOS图像传感器与色彩信号处理器集成到一个芯片内部的技术可以降低系统功耗和体积。由于MV86S02包含了图像采集的所有前端处理功能,并可以直接输出数字信号。因而大大方便了用户的使用,简化了开发工作,同时又提高了系统的性能。

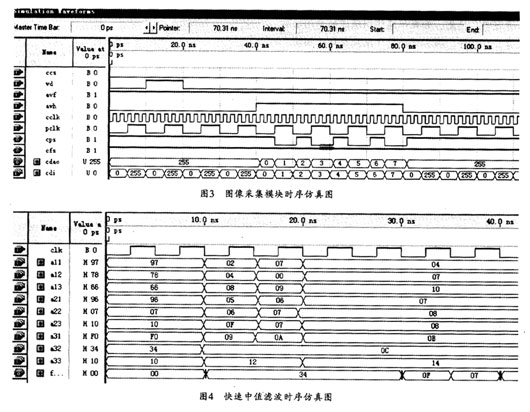

FPGA通过与7MB86S02型CMOS图像模块的连接,来通过VHDL程序将MB86S02所采集到的数字图像数据存储在SRAM中,以备后续的LCD显示和数据处理使用,然后还可以由UART模块或RTL8019模块把已经存储的图像数据发送到PC机,最后在PC机上的接收程序的控制下来显示接收的图像。图像采集模块的时序仿真结果如图3所示。

2 2图像低端处理模块

图像的低级处理工作的数据量很大,因而要求速度要快.但算法相对简单。本文在FPGA中实现了低端处理的中值滤波的快速处理算法的硬件电路,中值滤波窗口内所有像素点的度灰值都会从小到大(或O从大到小)顺序排列,并以度灰值序列的中间值来代替窗口中心像索点的灰度值。这就意味着执行过程中要进行大量的比较和赋值运算,改进的快速滤波算法的设计思想是将二维滤波阵列分解为一维来进行计算。即首先求出滤波窗口中水平各行像素点灰度值的中值,再求出这些水平各行中值的中值,并以此作为滤波结果。图4给出了快速中值滤波的时序仿真图。

2 3图像的高级处理和显示

高级的图像处理可以参考低级处理方式来实现。但运算的数据量较小,算法相对复杂,同时还具有一定的串行性。此次如继续用硬件实现,就要占用大量的硬件资源,因此,可以采用嵌入式的CPU来完成。由于CUu与FPGA的结构有很大的带宽,进行数据交换也很方便,因此,本文基于FPGA的可编程片上系统(SOPC)技术,将图像的高级处理由NiosⅡ核CPU结合定制指令和外围电路来实现,以提高处理速度,

而将图像显示叉由嵌入NiosⅡ处理器和VGA显示控制器来完成。

3结束语

以内嵌Nios软核的FPGA为核心处理器,可以完成图像的采集控制,低级,高级图像处理以及图像显示的设计。由于基于FPGA的可编程片上系统(SOPC)技术和大规模高性能的FPGA丰富资源。因此,利用嵌人NiosⅡ处理器和必要的外围电路,可使图像处理在速度、功耗、灵活性、开发周期和成本控制方面都得到很大的改进。

参考文献

[1] 景小军.图像处理技术及其应用[M].北京:国防工业出版社,2005

[2] 罗苑棠.CPLD/FPGA常用模块与综合系统设计 [M].北京:电子工业出版社,2007