摘要:高性能的数据压缩可以有效的减少数据对存储空间和通信带宽的要求,降低通信成本。为解决图像数据的高压缩性能问题,本文提出了基于JPEG2000标准的数据压缩系统的FPGA实现方案。相对于软件算法实现和其他硬件方法,采用FPGA硬件实现可降低系统复杂度提高性能。最终设计的IP核具有资源占用少,性能良好和便于扩展等优点,能够满足通信传输和照相设备等应用需求。

关键词:JPEG2000;数据压缩;FPGA;DWT

近年来通信领域中信息的传输总量急速扩大。由于存储空间有限、通信带宽等因素的限制,数据通常需要通过压缩才能有利于存储和传输,数字图像存储和传输的昂贵费用成为其普及的最大障碍。为此必须对数字图像压缩编码技术进行研究和实现。

JPEG2000标准采用的是离散小波变换,具有压缩率高和无边缘效应等优点。文中的设计采用片上系统(System On Claip)方案,可实现对分辨率1024x1024图像的压缩。在有效实现数据压缩基础上,系统还具有较好扩展性。研究利用FPGA实现图像数据压缩,将压缩算法映射到专用集成电路(ASIC)设计,具有非常广阔的市场应用前景。

1 基本原理

数字图像的压缩就是用一定的规律对需要处理的图像数据进行变换和排列,以尽可能少的数据信息来表示尽可能多的图像信息。图像的压缩是通过编码算法来完成实现的。目前常用的压缩方法有:图像变换技术、预测压缩、自适应压缩等方法。

图像数据之所以可以进行压缩,主要压缩来源于以下2点:一是在图像数据中存在大量信息冗余;另一点是人类的视觉观察精度是有限的通过减少数据精度来实现图像压缩。

在数字图像压缩中主要有:编码冗余、像素相关冗余和视觉心理冗余。通过算法减少或消除冗余就能实现图像压缩。另外根据人类视觉允许图像压缩后与原始图像有失真。图像压缩就是利用图像数据固有特性以及人类视觉特性,经过压缩算法提取有效的数据信息,减少数据信息量,以便实现高效率的图像数据传输和存储。

2 系统结构

根据JPEG2000标准,一般来讲基于JPEG2000标准的数据压缩系统主要由预处理、DWT、量化和EBCOT组成。组成结构如图1所示。

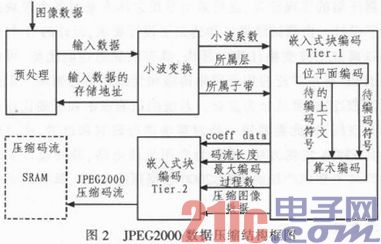

在参考JPEG2000标准数据压缩系统构架后,本文设计的数据压缩系统主要包括预处理,小波变换,量化和嵌入式位平面编码4部分,系统结构如图2所示。

预处理:对图像源数据进行划分,分成tile大小,之后进行DC位移和分量变换处理。

WDT:即小波变换把图像分解为空间频域子带具有能量更为集中,更好的压缩性能,而且可以很好的消除分块现象的优点。离散小波变换的提升算法可减少内存需求,降低计算复杂度。本文主要考虑提高压缩性能,因此采用的是9/7离散小波变换提升算法。

量化:将小波系数进行量化处理,之后按码块大小(32x32)储存量化后的小波系数,采用动态内存控制体制(DMC),降低小波系数缓存量。

EBCOT(Tier_1):对输入的子带小波系数进行底层嵌入式块编,并输出算术编码比特流和块编码的统计信息给Tier_2。

EBCOT(Tier_2):进行层生成及块信息编码,最终输出JPEG2000码流。

压缩编码过程如下:原始图像数据经过预处理变成许多个颜色分片(component—tile),每个分片经过小波变换后变成小波系数,量化后送入EBCOT进行编码和码率控制处理,为提高压缩速率,嵌入式为平面编码(EBCOT)模块采用并行处理结构,分别完成对前级量化后的小波系数HL、HH以及LH和LL的处理,小波系数在通过EBCOT模块进行编码和码率控制处理后,最后得到的是符合JPEG2000标准格式的压缩数据。

3 系统各组成模块的设计

本系统主要实现数据的压缩处理,源图像通过预处理模块对图像源数据进行划分,分成tile(512x512)大小,之后经过小波变换和EBCOT模块完成数据压缩处理,输出压缩码流。

3.1 预处理模块

由于原始图像数据较大,通过预处理模块可以大大降低数据对系统存储空间的要求。本文采用的预处理有:分片和电平平移,通过分片将原始图像分割成tile(512x512)大小的区块,每个分片进行独立压缩;电平平移使得图像数据关于零对称,有利于编码处理。

3.2 小波变换模块

采用离散小波变换对图像进行处理,得到图像的小波系数分为LL、LH、HL、HH 4个子带。通过级联,进行多级小波变换,小波系数中,高频数据分量表示图像中局部区域如图像的边缘,低频分量表示图像中的低频信息如图像的背景信息。可见通过小波变换,即使比特率不高的情况下,也能保证图像中较多的细节信息。图像通过小波变换时可进行不同级数的编解码处理,进而得到具有不同空间分辨率的图像信息。为实现较好压缩效果,需要对小波变换进行多次层分解,主要分解形式有:Mallat、Spacl和Packet,如图3所示。

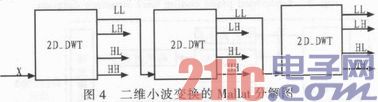

其中最为常用的分解方式为Mallat分解,每次分解实在对上一层的低频分量(LL)继续做Mallat分解,如图4所示。

一般来讲,多数设备是串行工作方式,图像数据普遍采用逐行的扫描方式,因此,在本文设计的数据压缩系统中,图像数据以逐行扫描方式输入DWT变换模块,小波变换采用9/7有损压缩,分解结构采用5层Mallat分解。

3.3 量化处理

人的视觉可分辨的图像是有一定范围的,因此通过适当量化减小数据精度实现对压缩。设计的量化步长决定了压缩效果的好坏。对图像量化操作是有损压缩,会产生一定的量化误差。量化后的图像数据都是由符号和幅值表示,量化后的系数在进行下一步的编码处理。

3.4 嵌入式块编码

在JPEG2000系统中,将量化后的子带划分成小的码块,认为码块间相互独立,以码块为单元,进行嵌入式编码。嵌入式编码的基本思想是通过计算适当的码流截断点,将压缩生成的码流划分成若干子集,每一子集表示对源图像的一个压缩。嵌入式码流可在任意一处被截断,得到具有不同码率或质量的重构图像。

在本设计中,模块采用了并行处理的方式来提高处理能力,嵌入式块编码分为Tier1和Tier2两部分:

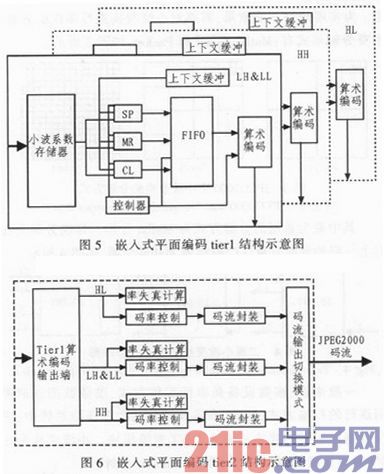

Tier1模块主要处理模块有:流程控制模块、比特平面编码、过程编码模块和算术编码模块,结构如图5所示。

工作流程是:首先,小波系数暂存于小波系数存储器中,然后进入EBCOT模块,对小波系数进行比特平面编码和过程扫描编码,进过处理的比特信息送入算术编码模块进行基于上下文的二进制算术编码。

Tier2模块主要功能模块有:率失真计算模块、码率控制模块和码流组织模块,结构如图6所示。

工作过程是:率失真模块完成编码块的失真率计算,传给后级模块,码率控制模块据此进行码流截断控制,之后给编码模块进行码流组织,不同子带方向上的码流合并输出JPEG2000压缩码流。

4 测试验证

文中设计的JPEG2000数据压缩系统在FPGA开发板上进行了验证,最终结果显示,可支持处理512x512大小16灰度级的tile图像分片,码块大小是32x32,实现对1 024x1 024的16灰度级的图像压缩处理,输入是图像数据信息,输出是符合JPEG2000标准的压缩码流。仿真时采用的工作时钟是50 MHz,对于1 024x1 024的16灰度级的图像完成16:1的压缩率,结果显示需要大约1 s左右的时间,满足设计要求。

5 结论

文中首先对JPEG2000标准进行了介绍,并详细分析了数据压缩的实现原理,之后给出系统总体方案对各个模块进行了设计。由测试结果可知达到了设计要求,设计的IP核采用以离散小波变换(DWT)算法,具有明显的性能优势,可代替JPEG标准广泛应用于网络传输和无线通讯等领域。但由于JPEG2000算法较为复杂,系统的压缩速率和压缩比还有提升空间,因此需要进一步对算法进行研究和改进,通过研究其FPGA实现方法,映射为专用集成电路,最终设计实现具有自主知识产权的JPEG2000数据压缩IP核,具有重要研究价值。