TI C2833x介绍---复位与中断(14)

时间:04-30 09:57 阅读:917次

*温馨提示:点击图片可以放大观看高清大图

简介:TI C2833x介绍---复位与中断(14)

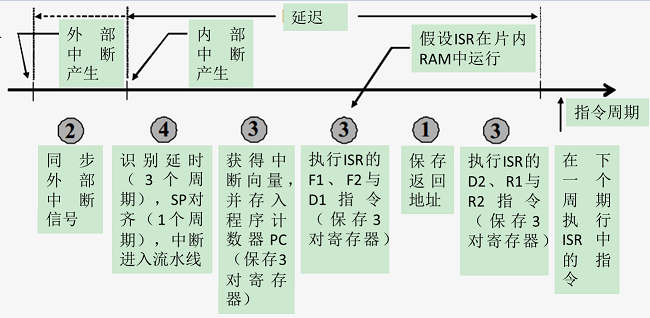

从中断事件产生,到CPU响应并开始执行中断程序ISR内的指令,需要以下几个周期的延时,如图所示:

可以计算出,

Ø 在响应内部中断的情况下:最少需要14个时钟周期

Ø 在响应外部中断的情况下:最少需要16个时钟周期

Ø 如果程序在外部存储器中运行,则需要更多的时钟周期

Ø 最长的延时则与CPU的等待状态、INTM寄存器的设置等有关

其中,图里面的D1,D2,F1,F2,R1,R2分别是CPU8级流水线处理过程中的6个阶段。

F1:CPU通过22位程序地址总线驱动程序存储空间

F2:CPU通过程序地址总线访问程序空间,并把指令放入取指令的序列

D1:读取序列中的指令,判断它是否是有效指令,并决定下次要读取的指令。

D2:从指令序列中请求一个指令,并完成解码操作。

R1:将所要读取的数据的地址传送到地址总线。

R2:从数据总线中读取数据。

Ps:CPU 8级流水线的另外2个阶段是:

E:指令的执行阶段,包括乘法、移位、ALU等操作。

W:写,即将数据写入存储器。