TI C2833x介绍---复位与中断(5)

时间:04-30 10:08 阅读:1094次

*温馨提示:点击图片可以放大观看高清大图

简介:TI C2833x介绍---复位与中断(5)

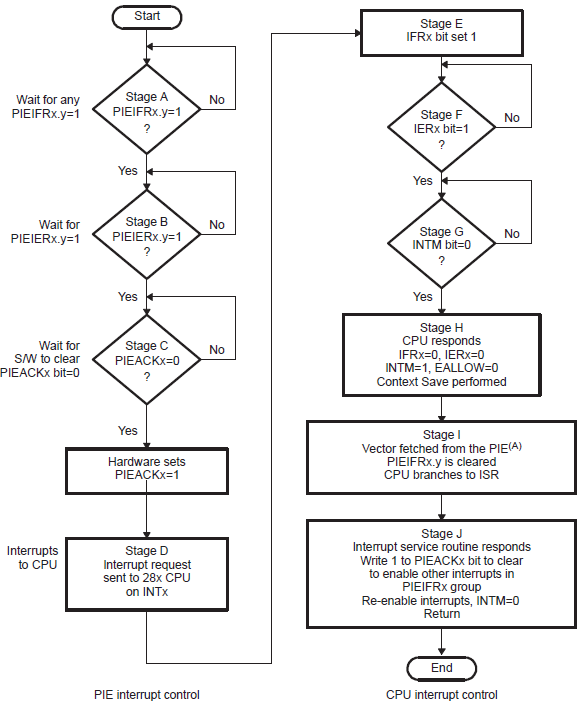

经PIE控制的中断的操作顺序:

(3) CPU级的操作

一旦PIE控制器将中断请求送入CPU,则CPU级的INTx对应的中断标志位(IFR)将被置位。一旦IFR中相应的标志位被锁存为1之后,除非满足下面的两种条件之一,否则对应的中断请求将暂时不会被响应:

1. CPU中断使能寄存器(IER)中对应的中断被使能

2. 调试中断使能寄存器(debug interrupt enable register,DBGIER)和全局中断屏蔽寄存器(global interrupt mask,INTM)中的该中断对应的相应位被使能。

总结前面的几个步骤,可以得到下面的流程图:

图1 PIE/CPU中断响应流程图INTx.y

那如果多个中断同时发出中断请求怎么办?当然,PIE首先响应优先级最高的那个,前提是它的中断标志位与使能位都已置位(就是说中断需要正确的配置好)。中断的来源很多,优先级貌似看起来很复杂,也不容易记忆,不过窍门也是有的:对于INTx.y,x越小,中断组的优先级越高;y越小,中断在该组内的优先级越高;先判断x的级别,然后判断y的级别。以前也没怎么注意这个规律,后来在程序中用到多个中断的时候没办法了,只好使劲读datasheet,结果很容易就发现这个规律了。

需要说明的是:在正常情况下,比如开发出来的一个产品中,debug相关的寄存器是不会使用的(不能让用户自己去debug),这样上面提到的流程中DBGIER这样的寄存器是没有用到的;这与我们使用仿真器来调试的时候使用的实时仿真模式是不同的。所以需要一个更加标准化的流程,放在下次讲。