摘要:在此设计的低成本手持式示波器是以ADC128S022模/数转换芯片为数据采集前端;使用FPGA片内双口内建RAM进行数据存储、有限状态机实现示波器的触发控制和显示驱动;最后再用LCD12864液晶模块完成终端的低成本图形显示。在DE0-Nano FPGA(Altera Cyclone IV)开发板上的测试结果表明,所设计的手持式示波器可以实现模拟信号任意电平上升沿或下降沿的触发测量;垂直灵敏度和扫描速度调节、波形参数的直接读出等功能。

关键词:FPGA;示波器;液晶显示屏;有限状态机

0 引言

目前,数字存储示波器以其体积小、携带方便、准确率高的独特优势逐步取代了传统的模拟示波器,并向着更为小巧的低成本、便携式应用方向发展。近几年来,许多研究者充分利用FPGA片上的资源丰富、使用灵活、开发成本低的优点提出了一些数字示波器的虚拟仪器解决方案和嵌入式解决方案,这些设计采用FPGA片内资源来实现数字示波器的数据存储(RAM)、触发控制、数字信号运算与处理、显示终端驱动等功能,这在很大程度上能够降低示波器成本和复杂度,但是这些设计方案往往会使用到微处理器(8051/ARM/NoisⅡ)作为系统调度和数据处理的核心或采用VGA显示器作为图形输出终端,还不能达到低成本的手持便携使用要求。

LCD12864液晶显示模块具有低压、微功耗、寿命长、超薄等显著优点,比较适合低成本、便携式电子信息产品来实现字符和图形的显示。因此,文中就以LCD12864液晶模块作为数字示波器的低成本图形显示终端;基于FPGA应用技术,设计出了具有模拟信号任意电平、上升沿或下降沿触发;垂直灵敏度和扫描速度调节、波形参数的直接读出特点的低成本手持式数字示波器。

1 手持式示波器的系统设计

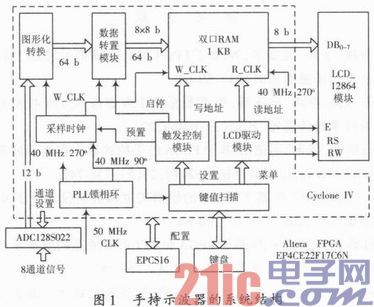

基于FPGA的手持式示波器系统结构框图如图1所示,系统主要包括片外AD芯片、配置芯片EPCS16、以及片内PLL模块、采样时钟配置模块、按键扫描模块、触发控制模块、双口RAM存储模块、采样数据图形化与转置模块、LCD12864显示驱动模块等。示波器的工作过程大致如下:经过片外ADC128S022采集的12 b数字信号,再经过片内图形化模块后转换成1列LCD屏显示的点阵数据;为了适应液晶屏按行读出的工作方式,需要通道数据转置模块把按列采样的点阵数据转置成按行排列的数据;触发模块主要是要根据用户设置(键盘输入)的触发电平及模式来控制RAM的写数据开始或停止指令,同时生成对应的写数据地址;数控采样时钟模块可以产生多种不同的采样时钟以满足不同频率信号的测量显示;LCD驱动模块主要是依据LCD的工作时序产生RAM的读数据地址和LCD模式控制指令。

图1所示手持式示波器的设计关键在于根据LCD12864显示模块的工作时序来组织双口RAM的读/写、片外A/D的数据采集;这样才能保证测量的模拟信号波形显示正确。下文就对片外A/D模块、双口RAM的读写控制和LCD显示驱动3个关键模块做出比较具体的设计描述。2 A/D转换模块

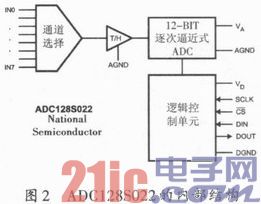

系统选用德州仪器公司(TI)的12位CMOS模/数转换芯片(ADC128S022)实现模拟信号的数据采样,该AD可以通过通道选择信号实现8通道的模数转换,并且是单电源供电;功耗极低,在2.7~5.25 V的供电范围内,功耗只有1.2~7.5 mW;转换速率可以达到50~200 KSPS,通过串行外设接口(SPI)与外部器件交换数据,芯片采用16引脚的超小型TSSOP封装,这些特征都很适合小型的便携式电子产品上使用,ADC12 8S022的内部结构如图2所示。

3 双口RAM的读写控制

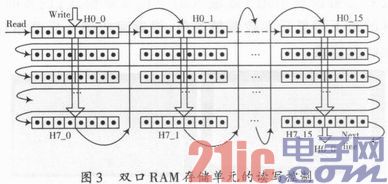

图1所示手持式示波器设计结构中的双口RAM的每位数据分别对应于LCD12864屏上的一个像素点,要求存储容量8 192 b(1 024×8 b)。存储器的管理需要满足采集数据(64 b)按列实时写入、又要满足LCD模块按行读出数据(8 b)的要求。

为此,首先需要把64 b的图形数据按位分成8段分别存储在8个128x8 b的RAM单元中,这样才能保证每个RAM存储单元的读/写数据位宽一致。其次,采集的波形数据需要经过行列数据转置模块,才能做到RAM数据的按行写入。行列数据转置模块采用了流水线结构,在触发启动信号和时钟的共同作用下把采集到的列点阵数据转置成适合LCD屏显示的行数据格式。

图3所示为双口RAM存储单元的读写顺序示意;经过转置后行数据,按照图中所示的横向“S”形顺序写入,而在数据读出时,需要按照逐行的竖向的“S”形顺序进行读数据,这是LCD12864模块控制时序要求的,按列逐字的写入存储器组织方式能够提高RAM的缓存数据刷新频率,同时也对存储器的读写地址生成电路形成了较高设计难度。4 LCD显示驱动模块

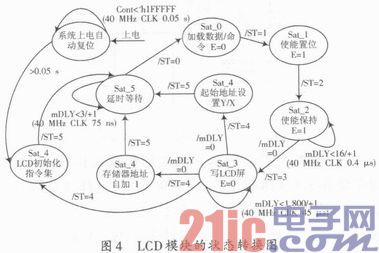

要驱动LCD模块显示正确图形,就需要根据液晶屏的控制时序和用户指令集,设计出正确的有限状态机(FSM)来完成LCD模块的初始化、控制命令和写入数据操作过程;并产生RAM读数据的地址,图4所示就是LCD显示驱动模块的状态迁移。

在LCD模块的状态转换图中,系统上电后,首先进行持续大约0.05 s的自动复位(需要根据时钟频率调整),然后进入LCD模块的初始化过程,因此在状态机中设置有3条条件转换路径来实现LCD屏的工作模式切换:初始化、显示数据和起始行地址写入。同时也在关键路径上设置有可以配置参数的延时——在方便LCD模块的工作调试的同时,使LCD模块一直工作在写屏模式,驱动LCD模块动态实时显示、产生双口RAM的

读数据地址。

5 设计验证

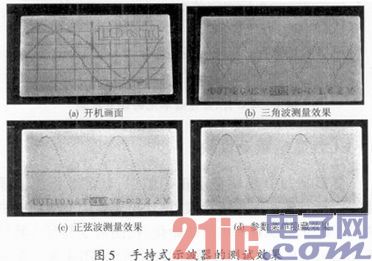

使用DEO_Nano开发板(Altera FPGA Cyclone IVEP4CE22F17C6N)、液晶模块(KB12864KZK)和4×4键盘组成手持式示波器的硬件测试验证平台;示波器设计项目经过OuartusⅡ10.1 FPGA开发平台的编译和芯片下载配置后得到的运行效果图如图5所示,图中(a)是手持式示波器开机的画面;(b)是三角波的测量效果;(c)是正弦波的测量效果;(d)是下拉菜单隐藏效果。示波器参数设置采用5键输入的下拉菜单模式;设置时,屏的最下端显示参数调整菜单,设置完成确认后菜单自动收起隐藏。

实验结果表明,采用LCD12864液晶模块作为手持式示波器的显示终端,虽然显示分辨率较低,可以清楚看到图形的像素点;同时,这也是采用LCD12864屏的独特优点所在——能够根据一个周期波形的像素点数和采样信号频率直接读出被测信号周期,假如采用100 kHz(周期10μs)的采样率;测得显示屏上的一个完整周期的波形点数是50,那么该被测信号的周期就是500 μs。

6 结论

文中所设计的以LCD12864模块为图形显示的低成本手持式示波器,最终在DEO_Nano FPGA开发板上的验证结果表明,完全实现了模拟信号的测量;垂直灵敏度和扫描速度调节、波形参数直接读出功能;这不但实现了示波器的廉价和便携,而且还具有被测信号周期直接读出的优点。