3 DDR200 的PCB 设计方法

下面以汽车音响导航系统中使用的DDR200为例,从PCB叠层结构的选择、布线拓扑结构、串扰、电源完整性和时序等方面考虑的PCB设计方法。

3.1 PCB叠层结构的选择

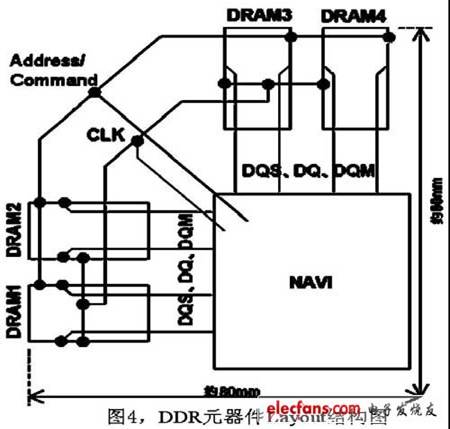

线路板的叠层结构直接决定了信号在各导体层的传输速度及延迟时间。根据电路构成及结构限制,结合高速信号及电源的返回路径等EMI要求,在设计初期确定好叠层结构以及重要信号的布线层是十分重要的。本例的叠层结构及重要信号的布线层如图3 所示。

根据板材不同, 导体铜厚, 各绝缘层厚及介电常数等也会有差异,导致高速信号传输线的特性阻抗Zo及传输延时Tpd的不同。

板材中绝缘介质的介电常数εr=4.0,绝缘层厚PP1=60μm,PP2=200μm,PP3=800μm,导体铜厚35μm,且线宽W=100μm时,信号在表层(L1、L6)的传输延时Tpd≒140ps,特性阻抗Zo≒56Ω,在内层L3布线的传输延时Tpd≒170ps,特性阻抗Zo≒84Ω。

3.2 DDR SDRAM信号的布线标准

为控制传输线的阻抗及延时等的影响, 要先确定以下的布线设计标准:

*高速信号线条宽度,以保证传输线特性阻抗值:差分信号Zo 100Ω,其他信号Zo≒50Ω。

*为减少传输线间的串扰,确定最小间距值。实际布线时要尽可能加大间距。

*可用过孔的孔直径及过孔焊盘直径:

①Build-up积层激光冲压孔②内层盲埋孔(L2到L5使用)③通孔(L1到L6用)④各种过孔焊盘间最小间距。

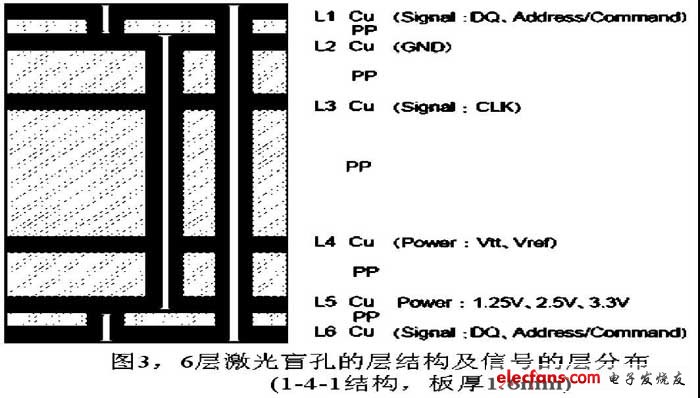

3.3 DDR SDRAM器件的布局结构图

DDR的数据传送通常是一个发射端对应多个接收端的结构, 为实现数据的同步传送,延迟时间的控制尤为重要。在构建器件Layout的时候重点考虑传输线分歧节点的选定,各段传输长度相等等要求。如图4,将DDR相关电路中的元器件都放在同一个面上, 并通过" 星型及Y 型拓扑结构"实现CLK、Data数据组,及Address/Command等各数据组之间的等长布线控制。