1引言

目前大多数温度采集系统都是利用智能温度传感器DS18B20和单片机来进行设计的。本课题尝试使用FPGA芯片进行设计。FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。鉴于此,本课题使用硬件描述语言设计FPGA控制器来实现传感器控制,同时用VC来实现用户控制界面。

现场可编程门阵列(Field Programmable Gate Array,FPGA)是当今应用最广泛的一类可编程专用集成电路(ASIC)。FPGA作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。电子设计工程师利用它可以在办公室或实验室里设计出所需的专用集成电路,从而大大缩短了产品上市时间,降低了开发成本。此外,可编程逻辑器件还具有静态可重复编程和动态在系统重构的特性。这使得硬件的功能可以像软件一样通过编程来修改,极大地提高了电子系统设计的灵活性和通用性。

本系统中温度传感器采用的MAXIM公司的1-Wire 器件DS18B20 温度传感器由于其结构简单、安装方便、功耗低、测温范围宽而被广泛的应用于化工、粮食、环境监测等需要实现多点测温的地方[3];1-Wire 技术采用一根信号线进行双向数据传输,一个控制器可以控制一个或多个从机设备,与其他标准串行数据通信方式如SPI、I2C 相比,单总线具有节省系统I/O 口线资源、结构简单、成本低廉、便于总线扩展和维护等诸多优点。

由于 1-Wire 总线只有一根信号线,所以要完成通信就要在一根信号线上实现数据的双向传输。1-Wire 通信协议对时序的要求非常严格,协议中一共规定了五种类型的通信时序,分别为初始化(复位)时序、写“1”时序、写“0”时序、读“1”时序和读“0”时序,如图1 所示。所有通信都由这五种典型时序组合完成,就是说要控制好这五种时序,才能实现对1-Wire 器件的控制。

2智能温度采集器的设计

采用可编程逻辑器件通过对器件内部的设计来实现系统功能,是一种基于芯片的设计方法。设计者可以根据需要定义器件的内部逻辑和管脚,将电路板设计的大部分工作放在芯片的设计中进行,通过对芯片设计实现数字系统的逻辑功能。灵活的内部功能块组合、管脚定义等,可大大减轻电路设计和电路板设计的工作量和难度,有效地增强设计的灵活性,提高工作效率。同时采用可编程逻辑器件,设计人员在实验室可反复编程,修改错误,以期尽快开发产品,迅速占领市场。

基于芯片的设计方法有很多有点,它可以减少芯片的数量,不必使用多个芯片,缩小系统体积,减少连线,降低出错几率,降低能源消耗,提高系统的性能和可靠性。在FPGA的设计中常用的设计方法有两种:自下而上和自上而下。几乎所有的复杂的数字系统的设计,都是可以按照层次进行细分的,将系统的层次按照功能逐步的进行细化,直到每一部分都有自己特定的功能并且不容易再进行分割为止。自上而下的设计方法非常重要,因为只有在上面的层次上才能全面确定下面模块的输入输出和功能行为的规格,并由此进行设计。自下而上的设计方法虽然并不太重要,但是有时也行得通,其原因是有些模块的规格本身是就是事先确定的或者基本可以确定的。

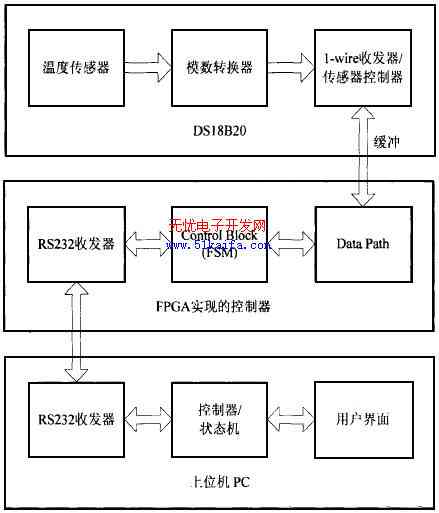

针对温度采集控制器系统的特点,决定采用自上而下的设计方法,并且将整个系统分为ControlUnit(控制模块)和Data Path(数据传输)两部分来进行设计(如图1所示)。这样设计有以下优点:(1)Control Unit在内部FSM的控制下,在每一个状态会有输出,控制Data Path中数据的传输,使其满足DS18B20的时序要求;(2)Data Path则完成了所有的数据流传输,并实时的反馈给Control Unit一些输入,从而使其状态转换能够正确完成;(3)如果要有附加的控制流和数据流要添加进整个FPGA系统,则只要在Control Unit中更改相应的状态和Data Path中做相应修改就可,不需要进行系统方案的修改。

图1、智能温度采集器的系统结构框图

在设计Control Block的时候一般采取有限状态机(FSM)的方法。FSM是指输出取决于过去输入部分和当前输入部分的时序逻辑电路。一个状态都有可以实现的进入条件,每个状态在所有输入条件下都有明确的下一状态,包括下一状态和目前状态相同的状态的情况。显然,如果下一状态只有和目前状态相同的状态才是可实现的,那么FSM一旦进入这个状态就不会再改变了,这种“死机”状态当然是要避免的。在此系统的 Control Block中的FSM采用摩尔型,设计出“下一状态逻辑”从而使得“状态寄存器”能在每一个时钟沿正确的进行状态转换,并确定好“输出逻辑”,在每一个状态都能输出正确的控制流来对 Data Path中的数据流进行正确的控制,保证整个系统能够正确的工作。

数据通道实现的是数据间的运算和传输。数据可能是8/16/32/64位的,一般有位的运算并没有太大的不同。但是,它又要同时实现Control Block中的FSM的功能,其设计是要和 Control Block中的FSM的结构一起考虑的。一旦FSM确定了,数据通道的计划就要着手进行。由于数据通道的性能决定了整个系统的性能的高低,所以它又非常的关键。以往通用处理器因为生产数量大,数据通道用全定制的方法设计比较多,线路和版图设计的精雕细刻,以求换得低的芯片生产成本和用其他方法难以达到的性能水平。这种情况在现代的SOC产品里有了很大的改变,因为SOC产品的产量一般都比较小,而且设计者都希望同一个处理器核的设计能够用于不同工艺生产的产品。这样,全定制的设计就不合适了。一般来说,数据通道是一定形式的流水线,因为数据的读取、运算和结果的写入都在同一个周期内实现,时钟频率就很难提高,所以高性能处理器的数据通道现在都采用流水线设计。数据通道和数据寄存器和数据存储器的关系十分密切,这当然是由处理器的结构确定的。在此系统中的 Data Path的数据流处理功能并不是非常的复杂,可以不用采取流水线设计,并在FSM的控制下进行正确的数据流传输,同时会反馈给FSM中的“下一状态逻辑”一些Inputs信号来使其能够进行正确的状态转换。

3智能温度采集器的实现

系统开发环境。本课题硬件设计采用XILINX公司SPARTAN-3器件开发板进行编程验证,其特性如下:(1)具有二十万门,十二个嵌入式18x18乘法器支持高性能DSP应用,216 Kbit的块RAM,50 MHZ内部时钟晶振;(2)板上2Mbit Platform Flash;(3)八个开关,四个按钮,八个LED,四个七段显示;(4)串口,VGA口,PS/两个鼠标/一个键盘口;(5)三组各40个引脚的扩展连接;(6)三个强电流的电压整流器(3.3V,2.5V,1.2V);(7)配合JTAG3编程线和Xilinx的P4&MultiPRO线。系统硬件设计采用Verilog HDL设计语言,设计流程在Xilinx公司提供的开发工具ISE中完成,配合MODELSIM SE仿真工具。SPARTAN-3开发板上使用MAX3222电平转换器,转换RS-232C的EIA电平+12V与TTL电平+3.3V。在本系统中,串口的波特率采用115200 bit/s,以达到其最快速度。上位机软件编程采用VC++ 6.0。

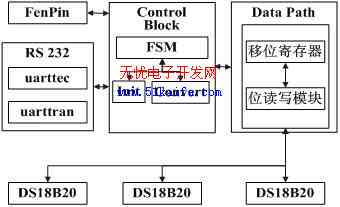

控制器逻辑功能流程图。首先设计各个硬件模块,其中主控模块状态机先只实现一些基本功能指令的流程控制,仿真测试单独的模块。然后连接各个模块组成完整的硬件电路并进行一些基本功能指令的测试。再串口调试助手及示波器检验硬件电路对一线总线上单个DS18B20的初始化(INITAILIZATION)、发送匹配ROM命令(MATCH ROM)、发送温度转换命令(CONVERT T)、发送引脚读取命令(READ SCRATCHPAD)、发送读时隙脉冲(READ TIMESLOTS)的操作结果。串口调试结果正确后联合上位机程序实现最基本的“Read Temperature”功能。上位机调试结果正确后硬件电路继续添加其他功能,调试“搜索ROM命令(SEARCH ROM)和读取ROM ID命令”,在FSM中实现搜索算法将温度采集扩展至一线总线上多个DS18B20。整个系统逻辑框图可见图2。

图2、智能温度控制器逻辑功能流程图

控制器逻辑功能模块。FPGA实现的控制器处于PC端上位机与温度传感器DS18B2O中间。FPGA的主要设计任务便是接收从串口得来的PC端上位机命令,通过内部状态机逻辑的判断和控制,通过Data Path将命令传达至温度传感器DS18B20,并将命令的执行结果返回给上位机。FPGA主要实现1-wire收发器和RS232收发器,对两边起沟通作用。整个硬件模块大致分成三层(图3),第一层为RS232串行通信模块和时钟分频模块fenpin,第二层为主控模块 Control Block,第三层为 Data Path部分:读/写模块bytebit。

图3、智能温度控制器系统模块层次结构图

l)RS232串行通信模块。负责外部上位机串行bit与主控模块Control Block并行byte间的数据传输。RS232串行通信速率采用 115200 bit/S。Uartrec从上位机接受一个字节com命令发给主控模块Control Block,同时Uarttran从主控模块Control Block接收一个字节result回应发给上位机。

2)分频模块fenpin。由50 MHZ内部晶振产生与DS18B20同步的1 MHZ时钟。

3)主控模块 Control Block。负责状态转化控制,实现 Data Path和RS232收发器的沟通。通过内部FSM逻辑的判断和控制,将命令传达至传感器,并将命令的执行结果返回给上位机。由两个延时子模块组成。初始化模块init,负责初始化总线上所有DS18B20,并在初始化成功后报告主控模块初始化状态。若初始化失败,将继续初始化。若超过设定初始化时间仍不能成功初始化,将停止初始化并报警。温度转化等待模块Convert,负责在读/写模块bytebit向DS18B20发出convert命令后延时800 ms再报告主控模块转化完毕。根据DS18B20用户手册,温度转化最多用750 ms。所以采用800 ms的保守估算。

4)Data Path。由读/写模块bytebit构成,负责主控模块Control Block和DS18B20之间的数据通信。由主控模块Control Block的r_w信号决定是发WRITE TIME SLOTS还是发READ TIME SLOTS。

4结束语

本系统采用FPGA和一线式数字温度转换器DS18B20来实现检测精度高,硬件结构简单,整个系统的速度快,灵活性高具有较强的抗干扰能力,不仅可以在汽车空调、医疗仪器等设备上进行单点温度测量,电路加以改动后还可以对粮食仓库,楼宇只能控制,煤矿等场合进行多点温度检测。